# 第一章 嵌入式系統架構

### 南台科大電子系 2005/5/10

# 1-1 前言

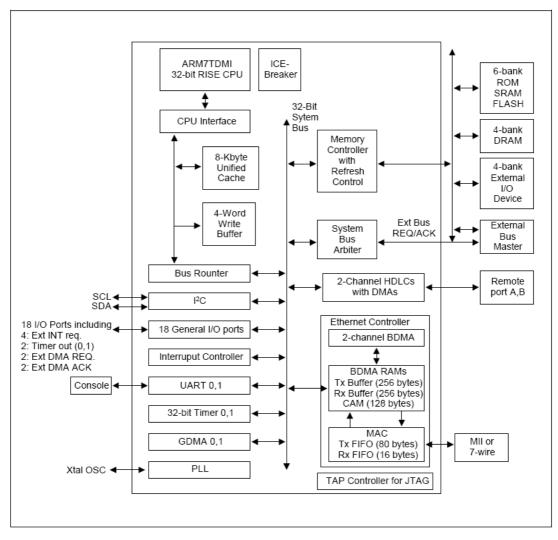

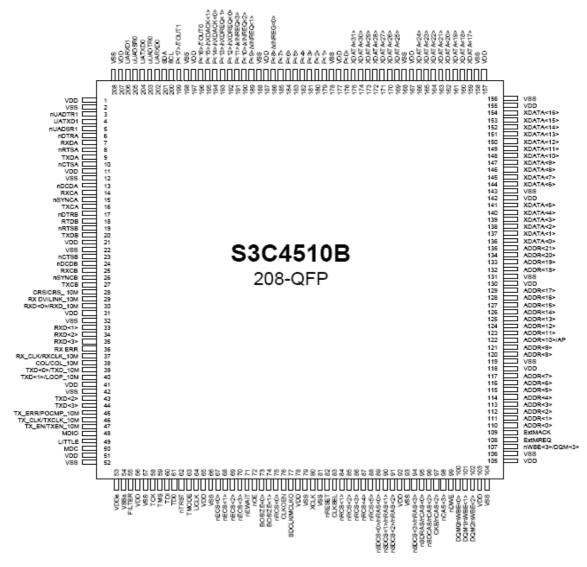

S3C4510B是一高性能、低功耗的32位元進階 RISC 處理器(Advanced RISC machine, 簡稱ARM)。以 ARM 為中央處理器所發展出來的低價位高效能 Linux 平台,可以充分利用 Linux 的豐富資源,在平台上發展各種應用,目前已支援 乙太網路(Ethernet)。Linux 提供多種系統功能供應用程式使用,加上Linux 跨平台的特性,發展applications 可以在一般桌上PC(x86)的 Linux C來發展,經編譯連結產生執行檔之後,再下載至本 ARM開發平台上執行即可。圖1-1與圖1-2分別為S3C4510B的功能方塊圖及接腳圖。

圖1-1 S3C4510B的功能方塊圖

圖1-2 S3C4510B的功能方塊圖

S3C4510B能外接記憶體,並且安裝具有uCLinux作業系統的核心程式於bank 0 Flash記憶體內,所以稱之為嵌入式系統(Embedded System)。目前來說嵌入式作業系統中包含有VxWORKs、Palm OS、Windows CE、Linux等,但成長最快的非微軟Windows CE作業系統而首推Linux,其原因如下:

### ■ 開放原始碼、模組化設計

Linux除了把原始碼公開以外,任何人都可以自由使用、修改、散佈,而 Linux核心本身採模組化設計,讓人很容易增減功能,例如我的平台並不需要藍 芽的功能,我只要不把這項功能加入,有需要就加入,不需要就刪除,由於這 樣的高的彈性,我們可以調校出最適合我們硬體平台的核心出來。

### ■ 穩定性夠

Linux不屬於任何一家公司,但是它的開發人員卻是全世界最多的,每天在全球都有無數的人參與Linux Kernel的改進、除錯、測試,這樣嚴苛的條件造就了穩定度高的Linux。

### ■ 網路功能強大

Linux的架構是參考UNIX系統而來,因此Linux也承襲了UNIX強大的網路功能。

### ■ 跨平台

Linux一開始是基於Intel 386機器而設計,但是隨著網路的散佈,各式各樣的需求湧現,因此就有許多工程師致力於各式平台的移植,造成了Linux 可以在x86、MIPS、ARM/StrongARM、PowerPC、Motorola 68k等平台上運作。

ARM Embedded System是將Linux作業系統成功的移植在以ARM處理器為核心的機器上,而其所運作的核心為uCLinux,uCLinux是Linux2.0作業系統的衍生程式,uCLinux精簡了Linux並保留Linux作業系統的穩定度。

# 1-2 uCLinux介紹

uCLinux是專爲無記憶體管理單元(Memory Management Units; MMU)的微控制器打造的嵌入式Linux作業系統。在uCLinux這個英文單詞中u表示Micro,小的意思,C表示Control,控制的意思,所以uCLinux就是Micro-Control-Linux,字面上的理解就是"針對微控制領域而設計的Linux系統"。

uCLinux的內核要比原Linux 2.0內核小的多,但保留了Linux作業系統的主要優點 --「穩定性」,優異的網路能力以及優秀的文件系統支援。以下幾點對 uCLinux作介紹:

### ■記憶體管理

這部分是uCLinux與傳統Linux區別最大的地方。標準Linux是針對有MMU的處理器設計的。對於uCLinux來說,其設計針對沒有MMU的處理器,即uCLinux不能使用處理器的虛擬記憶體管理技術。由於沒有MMU管理,所以uCLinux對於記憶體的存取是直接的,作業系統對記憶體空間沒有保護,各個進程實際上共用一個運行空間,用戶程式同內核以及其他用戶程式在一個位址空間,程式開發時要保證不侵犯其他程式的位址空間,以使得程式不至於破壞系統的正常工作,或導致其他程式的運行異常。

#### ■ uCLinux的核心程式載入方式

uCLinux的核心程式有兩種可選的運行方式:可以在flash上直接運行,也可以載入到記憶體中運行。後者可以減少記憶體需要。

- 1. Flash運行方式:把可執行文件燒到flash上,系統啟動時從flash的某個地址 開始逐句執行。這種方法實際上是很多嵌入式系統採用的方法。

- 2. 直接載入到記憶體中運行:把壓縮文件存放在flash上,系統啟動時讀取壓縮文件在記憶體裏解壓,然後開始執行,這種方式相對複雜一些,但是運

行速度可能更快(RAM的存取速率要比Flash高)。同時這也是標準Linux 系統採用的啓動方式。

#### ■ uCLinux的應用程式庫

uCLinux小型化的另一個做法是重寫了應用程式庫,相對於越來越大且越來越全的glibc庫,uCLinux的應用程式庫uClibc對glibc做了精簡。uCLinux對用戶程式採用靜態鏈結的形式,這種做法會使應用程式變大,但是基於記憶體管理的問題,也就是基於沒有MMU的特性,只能這樣做,同時這種做法也更接近於通常嵌入式系統的做法。

#### ■ 可執行文件格式

uCLinux系統使用flat可執行文件格式,由於uCLinux針對無MMU處理器開發,所以被迫使用一種flat方式的記憶體管理模式,啓動新的應用程式時系統必須爲應用程式分配存儲空間,並立即把應用程式載入到記憶體。而elf(excutive linked file)爲Linux系統所採用的通用文件格式,elf格式有很大的文件頭,flat文件對elf格式文件頭和一些段資訊做了簡化後,佔用的空間變小更適用於嵌入式系統。

對於uClinux共有以下幾個主要的特色:

- 通用的Linux 應用程式介面(Application Program Interface, 簡稱API)

- 核心程式(kernel)小於<512 KB

- 核心程式 + 發展工具程式小於 900 KB

- 完整的TCP/IP協定堆疊

- 支援大量其他的網路協定

由於uCLinux為一開放性自由軟體,並支援大量網路協定功能,其佔用空間小,對於目前消費性產品要求成本低、佔用佔用空間小、功能強的需求可說是一最佳選擇。

# 1-3 記憶體及外部I/O的讀寫

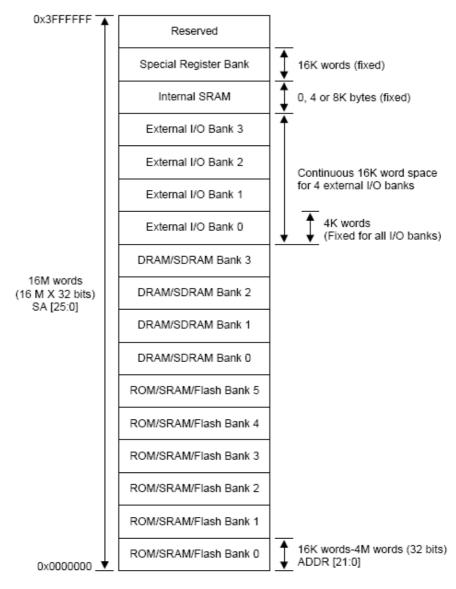

S3C4510B的內部記憶體及暫存器可參考圖1-3的說明。S3C4510B的

NOTE: You can define banks anywhere within the 64-Mbyte address space.

圖1-3 S3C4510B 的內部暫存器及記憶體

有4個bank DRAM/SDRAM 以及6個bank ROM/SRAM/Flash,每個Bank可由位址線ADDR21-ADDR0所定址,所以每個Bank的最大定址空間為4Mbyte。 S3C4510B也有具有4個bank I/O。DRAM、Flash/ROM/SDRAM 以及I/O 的起始位址可透過S3C4510B的特殊暫存器(Special Register)來規劃。這些特殊暫存器的規劃方法可分別參考S3C4510B使用手冊的P4-49、 P4-36、P4-49以及P4-61。研廣 ARNUX7525A 是我們選用的S3C4510B的嵌入式開發平臺。此開發平臺開機程式自動設定4個bank DRAM、6個bank Flash位址分佈如圖1-4。

| 0x3FF0000 - 0x3FFFFFF | System Register     |

|-----------------------|---------------------|

|                       |                     |

| 0x760C000 - 0x760FFFF | External IO 3 (64K) |

| 0x7608000 - 0x760BFFF | External IO 2 (64K) |

| 0x3604000 - 0x3607FFF | External IO 1 (64K) |

| 0x3600000 - 0x3603FFF | External IO 0 (64K) |

|                       |                     |

| 0x1000000-0x1FFFFFF   | DRAM 0 (16M)        |

|                       |                     |

| 0x0400000 - 0x07FFFFF | ROM 1 (4M)          |

| 0x0000000 - 0x03FFFFF | ROM 0 (4M)          |

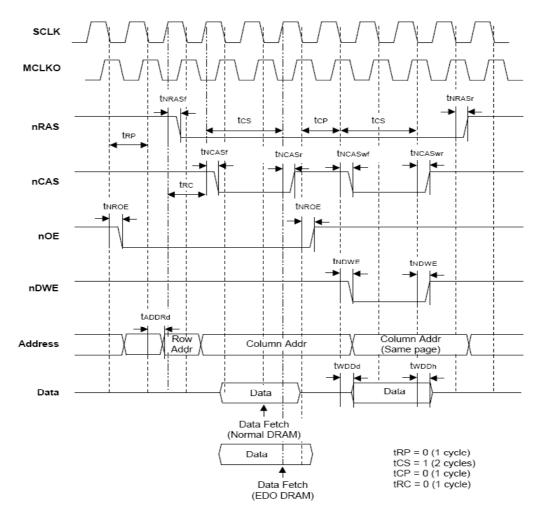

圖1-4 研廣 ARNUX7525A 開發平臺的內部暫存器及記憶體位址分佈 記憶體每個bank是由位址線ADDR21~ADDR0所定址。因此每個記憶體bank最大容量是4M。讀寫DRAM時,由指定位址解碼使須

- 1. 代表4個DRAMbank的致能線 nSDCS[3:0]其中之一條線出現低電位。

- 2. 列位址致能線nRAS[3:0]及行位址致能線nCAS[3:0] 的其中之一條線出現低電位。讀寫時序如圖1-5所示。

# 圖1-5 DRAM讀寫時序圖

DRAM 4個bank的寫入致能線皆為nDWE (I/O寫入致能線是用nWBE[3:0])。記億體及四個bankI/O讀取致能線皆共用訊號線nOE。

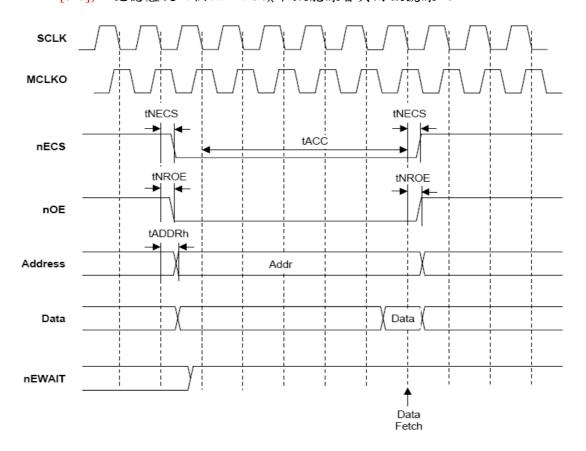

圖1-6 I/O讀取時序

ARM 4個I/O bank,每個I/O bank致能訊號線是nECS[3:0]。I/O讀寫時序圖1-6及圖1-7所示。

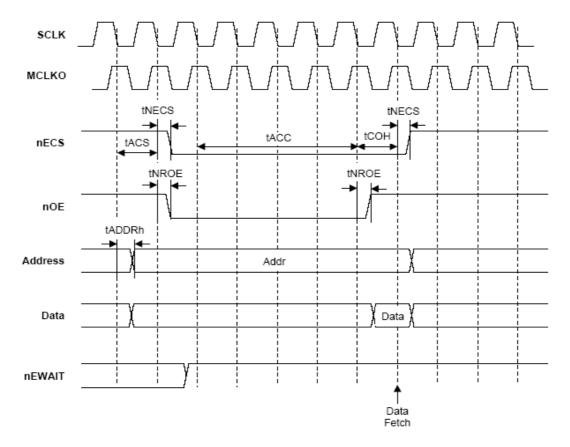

圖1-7 I/O寫入時序

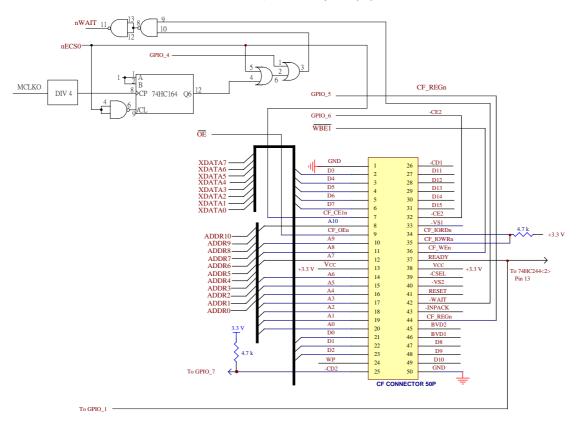

圖1-8 具有nWAIT低電位時間的參考電路

I/O讀寫時間可由系統暫存器EXTACONO及EXTACON1來設定。S3C4510B內部時脈為50 MHz,當讀寫時間需200 nS以上時,無法透過EXTACONO或EXTACON1來設定。I/O讀寫時間長短,除了上述方法外,也可透過nEWAIT訊號線來彈性調整。nEWAIT沒有使用時空接即可。圖1-8為CF卡與S3C4510B連接的參考電路。當GPIO\_4=1時,nWAIT低電位時間由CF卡發出的-WAIT訊號線低電位時間所決定。當CF卡-WAIT訊號線不會產生低電位,但讀寫時間需200 nS以上時,可令GPIO\_4=0,此時nWAIT低電位時間約為7個 $T_{CLK4}$ 週期時間,其中 $T_{CLK4}$ =4× $T_{CLK}$ 1500 MHz。

| Registers | Offset | R/W | Description                 | Reset Value |

|-----------|--------|-----|-----------------------------|-------------|

| EXTDBWTH  | 0x3010 | R/W | Data bus width of each bank | 0x00000000  |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

#### EXTDBWTH 0

# 0 0 0 DSX3 DSX2 DSX1 DSX0 DSD3 DSD2 DSD1 DSD0 DSR5 DSR4 DSR3 DSR2 DSR1 DSR0

#### [1:0] Data bus width for ROM/SRAM/FLASH bank 0 (DSR0)

DSR0 is read-only data at the B0SIZE [1:0] pins. DSR0 is used as read-only because ROM/SRAM/FLASH bank 0 is used to boot the ROM while the data bus width for ROM/SRAM/FLASH bank 0 is set using B0SIZE [1:0].

00 = Not permitted

01 = Byte (8 bits)

10 = Half-word (16 bits)

11 = Word (32 bits)

#### [3:2] Data bus width for ROM/SRAM/FLASH bank 1 (DSR1)

### [5:4] DSR2, [7:6] DSR3, [9:8] DSR4, [11:10] DSR5

00 = Disable

01 = Byte (8 bits)

10 = Half- word (16 bits)

11 = Word (32 bits)

#### [13:12] Data bus width for DRAM bank 0 (DSD0)

#### [15:14] DSD1, [17:16] DSD2, [19:18] DSD3

00 = Disable

01 = Byte (8 bits)

10 = Half-word (16 bits)

11 = Word (32 bits)

#### [21:20] Data bus width for external I/O bank 0 (DSX0)

### [23:22] DSX1, [25:24] DSX2, [27:26] DSX3

00 = Dissable

01 = Byte (8 bits)

10 = Half-word (16 bits)

11 = Word (32 bits)

NOTE: When you select "Disable", the assigned external I/O

bank access signal is not generated.

### 圖1-9 EXTDBWTH暫存器的格式

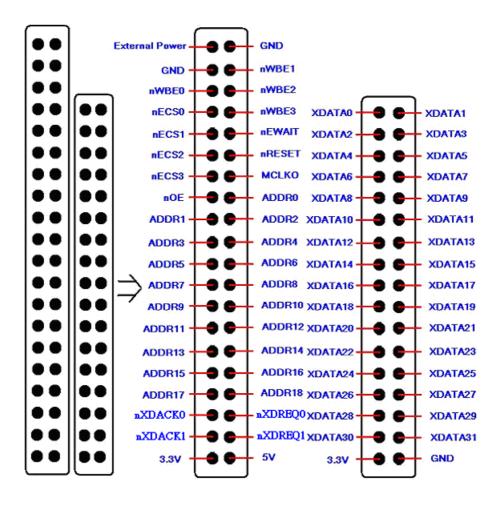

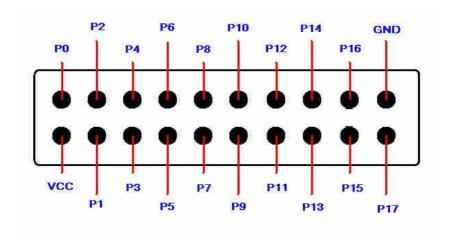

ARM7有32條資料線,可透過EXTDBWTH暫存器規劃成8位元、16位元及32位元三種模式。EXTDBWTH暫存器格式請參考圖1-9。研廣公司所提供的發展板將位址線、資料線及相關控制線轉接出來。訊號線排列方式請參考圖1-10。

圖1-10 ARNUX轉接槽 Pin 腳圖

### ARNUX 擴充槽 Pin 腳說明:

| Pin Name      | Type   | Descriptions                                                                                                                                                                                                                                                                |

|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nWBE0 ~ nWBE3 | Output | Not Write Byte Enable. Whenever a memory access occurs, the nWBE output controls the write enable port of the specific memory device (except for DRAM). For DRAM banks, CAS[3:0] and nDWE are used for the write operation. DQM is data input/output mask signal for SDRAM. |

| nECS0 ~ nECS3 | Output | Not External I/O Chip Select. Four external I/O banks are provided for external memory-mapped I/O operations. Each I/O bank stores up to 16 Kbytes. nECS signals indicate which of the four external I/O banks is selected.                                                 |

| nOE           | Output | Not Output Enable. Whenever a memory access occurs, the nOE                                                                                                                                                                                                                 |

|                                  |                | output controls the output enable port of the specific memory device.                                                                                                                                                                                                                                                             |

|----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR0 ~ ADDR18                   | Output         | Address Bus. The 19-bit address bus, ADDR[18:0], covers the 512K word address range of the external I/O banks.                                                                                                                                                                                                                    |

| XDATA0 ~ XDATA31                 | Input / Output | External (bi-directional, 32-bit) Data<br>Bus. The S3C4510B data bus supports<br>external 8-bit, 16-bit, and 32-bit bus<br>sizes.                                                                                                                                                                                                 |

| nEWAIT                           | Input          | Not External Wait. This signal is activated when an external I/O device or ROM/SRAM/flash bank 5 needs more access cycles than those defined in the corresponding control register. When de-assert the nEWAIT, you must synchronize the nEWAIT with MCLKO rising edge. If not, memory state machine can get into the Wrong State. |

| nRESET                           | Input          | Not reset. nRESET is the global reset input for the S3C4510B. To allow a system reset, and for internal digital filtering, nRESET must be held to low level for at least 64 master clock cycles. Refer to "Figure 3. S3C4510B reset timing diagram" for more details about reset timing.                                          |

| MCLKO                            | Output         | System clock out. MCLKO is monitored with some delay as the same phase of internal system clock, MCLK(SCLK). SDCLK is system clock for SDRAM.                                                                                                                                                                                     |

| nXDACK0 ~ nXDACK1 /<br>P14 ~ P15 | Input / Output | Not external DMA acknowledge from GDMA or general I/O ports.                                                                                                                                                                                                                                                                      |

| nXDREQ0 ~ nXDREQ1 /<br>P12 ~ P13 | Input / Output | Not external DMA requests for GDMA or general I/O ports.                                                                                                                                                                                                                                                                          |

| External Power                   | Output         | The output voltage is almost the same as the one of DC Adapter. This pin is internally connected with DC Power input pin directly except through a diode.                                                                                                                                                                         |

| 3.3V                             | Output         | 3.3V / 50mA voltage output.                                                                                                                                                                                                                                                                                                       |

| 5V                               | Output         | 5V / 50mA voltage output.                                                                                                                                                                                                                                                                                                         |

| GND                              | GND            | Power ground.                                                                                                                                                                                                                                                                                                                     |

# 1-4 廣泛用途的I/O位元(GPIO bits)

ARM7有18 位元GPIO(General Purpose I/O),這些位元定義可參考圖1-11,排列方式參考圖1-12,位置參考圖1-16(a)L。這個GPIO也可當做中斷要求,DMA要求/認可及計時器輸出使用。若當做一般I/O bit使用,將IOPCON暫存器對應位元寫入0。反之,若作其他功能,對應位元寫入"1"。若某些位元當做一般GPIO使用,透過IOPMOD暫存器規劃為Input或output模式。真正18位元GPIO存取是透過 IDPDATA暫存器存取。IOPCON、IOPMOD及IDPDATA暫存器分別參考圖1-13、圖1-14及圖1-15。

| Port   | I/O Type | Descriptions                                   |

|--------|----------|------------------------------------------------|

| Number |          |                                                |

| P[0]   | I/O      | General Input/Output Port (GPIO)               |

| P[1]   | I/O      | General Input/Output Port                      |

| P[2]   | I/O      | General Input/Output Port                      |

| P[3]   | I/O      | General Input/Output Port                      |

| P[4]   | I/O      | General Input/Output Port                      |

| P[5]   | I/O      | General Input/Output Port                      |

| P[6]   | I/O      | General Input/Output Port                      |

| P[7]   | I/O      | General Input/Output Port                      |

| P[8]   | I/O      | External interrupt request line or             |

|        |          | general Input/Output Port                      |

| P[9]   | I/O      | Ext. interrupt request line or GPIO            |

| P[10]  | I/O      | Ext. interrupt request line or GPIO            |

| P[11]  | I/O      | Ext. interrupt request line or GPIO            |

| P[12]  | I/O      | Not ext. DMA requests 0 or GPIO                |

| P[13]  | I/O      | Not ext. DMA requests 1 or GPIO                |

| P[14]  | I/O      | Not ext. DMA acknowledge from GDMA or GPIO     |

| P[15]  | I/O      | Not external DMA acknowledge from GDMA or GPIO |

| P[16]  | I/O      | Timer 0 out or GPIO                            |

| P[17]  | I/O      | Timer 1 out or GPIO                            |

圖1-11 GPIO Pin腳定義

圖1-12 GPIO Pin 腳圖

| Register | Offset Address | R/W | Description               | Reset Value |

|----------|----------------|-----|---------------------------|-------------|

| IOPCON   | 0x5004         | R/W | I/O port control register | 0x00000000  |

| 31 30 29 28 | 27 26 | 25 23 | 22 20 | 19 15     | 14 10            | 9 5              | 4 3 2 1 0        |

|-------------|-------|-------|-------|-----------|------------------|------------------|------------------|

| T OE N 1    | DAKO  | DR Q1 | одио  | X - R Q 3 | X<br>R<br>Q<br>2 | X<br>R<br>Q<br>1 | X<br>R<br>Q<br>1 |

#### [4:0] Control external interrupt request 0 input for port 8 (xIRQ0)

[4] Port 8 for xINTREQ0

0 = Disable [3] 0 = Active Low 1 = Enable 1 = Active High [2] 0 = Filtering off 1 = Filtering on

[1:0] 00 = Level detection 01 = Rising edge detection 10 = Falling edge detection 11 = Both edge detection

#### [9:5] Control external interrupt request 1 input for port 9 (xIRQ1)

(See control external interrupt request 1.)

#### [14:10] Control external interrupt request 2 input for port 10 (xIRQ2)

(See control external interrupt request 2.)

# [19:15] Control external interrupt request 3 input for port 11 (xIRQ3)

(See control external interrupt request 3.)

### [22:20] Control external DMA request 0 input for port 12 (DRQ0)

[22] Port 12 for nXDREQ0

0 = Disable 1 = Enable [21] 0 = Filtering off 1 = Filtering on [20] 0 = Active Low 1 = Active High

# [25:23] Control external DMA request 1 input for port 13 (DRQ1) [25] Port 13 for nXDREQ1

0 = Disable [24] 0 = Filtering off [23] 0 = Active Low 1 = Filtering on 1 = Active High

# [27:26] Control external DMA acknowledge 0 output for port 14 (DAK0) [27] Port 14 for nXDACK0

0 = Disable 1 = Enable [26] 0 = Active Low 1 = Active High

# [29:28] Control external DMA acknowledge 1 output for port 15 (DAK1) [29] Port 15 for nXDACK1 0 = Disable 1 = Enable

[28] 0 = Active Low 1 = Active High

#### [30] Control timeout 0 for port 16 (TOEN0)

0 = Disable 1 = Enable

#### [31] Control timeout 1 for port 17 (TOEN1)

1 = Enable 0 = Disable

圖1-13 IOPCON暫存器的格式

| Register | Offset Address | R/W | Description            | Reset Value |

|----------|----------------|-----|------------------------|-------------|

| IOPMOD   | 0x5000         | R/W | I/O port mode register | 0x00000000  |

[0] I/O port mode bit for port 0

0 = Input

1 = Output

[1] I/O port mode bit for port 1

0 = Input

1 = Output

[2] I/O port mode bit for port 2

0 = Input

1 = Output

[17] I/O port mode bit for port 17

0 = Input

1 = Output

圖1-14 IOPMOD暫存器的格式

| Register | Offset Address | R/W | Description            | Reset Value |

|----------|----------------|-----|------------------------|-------------|

| IOPDATA  | 0x5008         | R/W | I/O port data register | Undefined   |

[17:0] I/O port read/write values for ports 17-0 (P0-P17)

NOTE:

The values in the I/O port data register reflect the signal level on the respective I/O port pins. When the ports are configured to output mode, the bit reflects the ports write value. When the port is configured to input mode, the bit reflects the ports read value.

圖1-15 IOPDATA暫存器的格式

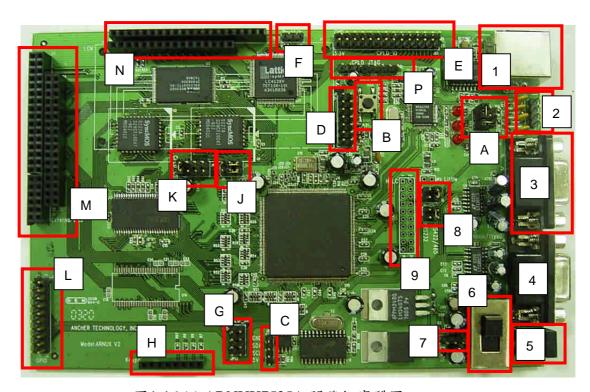

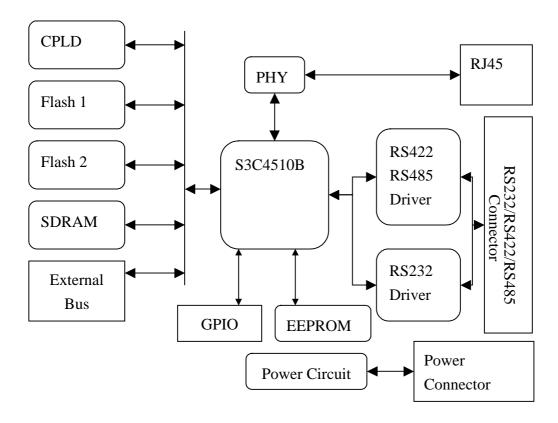

# 1-5 ARM7開發平臺

研廣 ARNUX7525A 是我們選用的ARM7的嵌入式開發平臺。ARNUX7525A 套件由開發板和開發工具光碟組成,開發板上具有ARM7處理器,16MB (可擴充到 32MB) SDRAM 以及 4+1MB 的 FLASH,為用戶的軟體研發提供了足夠的空間。開發板上提供豐富的外部介面:一個 10M / 100M 自動偵測快速乙太網介面、兩個 RS-232 串列 Port、一個 IIC Bus、一個 JTAG Debug Tool、以及將ARM7訊號線外接所需的擴充槽。開發板即構成一個最小的完整

應用系統。系統具有體積小、耗電低、處理能力強、網路功能強大等特點,能夠裝載和運行嵌入式 Linux 作業系統。用戶可以在這個系統平臺上進行自主軟體發展,並對 ARNUX 進行測試和評估,也可在保持核心板不變的情況下,針對具體的應用透過對開發板的更改來實現自己的應用系統。

另外,一般在桌上PC(x86) Linux 上面能夠執行的 Server 軟體,亦可只要經過適度的修改,就可以在這個平台上使用。像是 web server,database,samba,IP forward,sniffer 等等各種網路 server 應用程式。I/O 部分經過擴充之後,再配合 Linux 驅動程式,便可以連接 hard disk,記憶卡,LCD module,video in/out 等等各種硬體。在這個平台上配合適度的額外硬體與軟體,便可以發展各種低中高階的應用,如 Mail Server、Ftp Server、File Server、Web Server、Proxy、Gateway、MP3 Player 等等。若是需要更高的處理效率,像是影像處理等等,更可以增加 DSP 等晶片作更高階的應用。

圖1-16(a) ARNUX7525A 開發板實體圖

圖1-16 (b) ARNUX7525A 開發板功能方塊圖

| 項目 | 說明                                        |

|----|-------------------------------------------|

| 1  | Ethernet RJ45 Connector                   |

| 2  | RS422/RS485 Connector                     |

| 3  | /dev/ttyS1 Connector                      |

| 4  | Console or /dev/ttyS0 Connector           |

| 5  | Power Input                               |

| 6  | Power Switch                              |

| 7  | Power Input (5V, 3.3V, GND)               |

| 8  | JP3, JP11 (RS232 or RS422/RS485 Selector) |

| 9  | HDLC Connector                            |

| A  | RS422 or RS485 Selector                   |

| В  | Reset Button                              |

| С  | IIC Connector                             |

| D  | ARM7 JTAG Connector                       |

| Е  | CPLD IO Connector                         |

| F  | LCM Back Light                            |

| G  | CPLD Interrupt Selector                   |

| Н  | Key Pad Connector                         |

| J  | Flash Selector                            |

| K | CPLD Chip Selector  |

|---|---------------------|

| L | GPIO                |

| M | External BUS        |

| N | LCM Connector       |

| P | CPLD JTAG Connector |

# 詳細特點

|       | 16/32-bit RISC microcontroller                                  |

|-------|-----------------------------------------------------------------|

|       | 4+1MB Boot ROM                                                  |

|       | One ( or Two ) 2MBx16 with 4 banks SDRAM                        |

|       | GPIO(General Purpose Input/Output)                              |

|       | Two serial ports , one for console( up to 115200 bps) , one for |

|       | RS232/RS422/RS485                                               |

|       | IIC-bus EEPROM                                                  |

|       | 10/100Mbps Ethernet interface ( auto-negotiation )              |

|       | JTAG for EmbeddedICE <sup>TM</sup> Interface                    |

|       | HDLC(high-level data link controllers) interface                |

|       | 18x2 Alphanumeric (9x2 繁體中文) LCM                                |

|       | 4x4 Keypad                                                      |

|       | Lattice 128 macrocells CPLD (LC4128V)                           |

|       | 精簡而完備的 uClinux kernel (Ver 2.0.38)                              |

|       | 高性能而穩定性良好                                                       |

|       | 多工的環境                                                           |

|       | 可自訂開機流程                                                         |

|       | 可發展 ARM7 組合語言程式                                                 |

|       | 應用系統相容性佳                                                        |

|       | 設備的獨立及高安全性                                                      |

|       | 成本低                                                             |

|       | 支援TCP/IP                                                        |

|       | GNU GCC 編譯器支援 ANSI C 、 K&R C 、 C++ 、 Object C                   |

| JP1 用 | 來調整 ROMO 以及 ROM1 的記憶體。JP1 的所在位置請參考 7 Pin                        |

| 腳定義。  |                                                                 |

17

圖1-17 JP1 的排列

當 JP1 的 Jumper 裝在 Pin1, Pin2 的時候,會使用安全模式,也就是 1M 的 Flash 開機。而裝在 Pin2, Pin3 的時候,會使用使用者模式,也就是 4M 的 Flash 開機。一般而言 1M 的 Flash 放著出貨時可以開機以及更新 Flash 的 Linux 映像檔,可以在使用者燒錄自己的映像檔發生問題時,用來重新燒錄使用。以上過程,與內部所附的燒錄軟體 flashwrite 有相關連:

在使用者模式下 (Pin2, Pin3) 燒錄 4M Flash, flash type 應選擇 1

#flashwrite 1 IMGNAME CHECKSUM

在安全模式下 (Pin1, Pin2) 燒錄 4M Flash, flash type 應選擇 2

#flashwrite 2 IMGNAME CHECKSUM

程式設計時,相關的各暫存器(Registers)位址及硬體I/O參考資料,可參考 Samsung 網站所下載來的二份技術資料(光碟片中有收錄)。 "旗標出版 施威銘 研究室著--LINUX C 語言實務" 這本書中可做為開發C語言初級應用程式時參考。進階的程式開發可參考"文魁出版 洪錦魁著--UNIX C 語言入門與應用徹底研究"。"旗標出版 徐千洋著--LINUX C 函數庫參考手冊" 這本書中的常用的C 函數大多都有支援[但 fork() 改成 vfork(),及確定無提供 brk()和sbrk() 函數,並要注意fork()和vfork()有一點不一樣。]

# CPLD 說明及 CPLD I/O 擴充

CPLD 提供額外的 I/O 以及 Key Pad 與 LCM 的控制使用,此外,也處理部份的系統 Reset 線路。CPLD 可以提供使用者自行規劃的功能,硬體上,將 ARM7 的位址,資料匯流排,讀寫訊號,甚至是中斷要求都有接到 CPLD上面。

由 CPLD 擴充 13 個 Input 以及 13 個 Output,其中 J13 的 Pin1,Pin3 則與LTC491 的 輸出入控制共用。J13 的外排 Pin 都是輸出,內排 Pin 則是輸入。CPLD 的 CS 可以由 JP12 來決定使用哪一個 ECS,CPLD 的控制位址為

EXTERNAL\_IO\_OFFSET\_ADDRESS + 0x00 Key data

EXTERNAL\_IO\_OFFSET\_ADDRESS + 0x20 IO (7..0)

EXTERNAL\_IO\_OFFSET\_ADDRESS + 0x24 IO (12 .. 8)

EXTERNAL\_IO\_OFFSET\_ADDRESS 請參考 Memory Mapping 部分的說明。 CPLD 可以透過 CPLD\_JTAG(J12) 重新規劃,但是有幾個地方需要注意。

- 1. 系統的 Reset 電路也是透過 CPLD 來控制,因此 Reset 部分的邏輯必須要維持,否則可能出現無法開機現象。

- 2. 資料與位址線,不能在 CPLD 規劃時隨意設計,需要合乎整個系統的時脈。 部分系統訊號 (Interrupt, MCLKO 等等) 都有訊號接入 CPLD 中,可以在重新規 劃時使用所需要的訊號。中斷訊號只有一 Pin,但可以由 JP13 加以選擇。

# /dev/ttyS1 RS232/RS422/RS485 使用

JP10,JP11 將 Jumper 裝在 RS232 端,則使用 RS232 功能。JP10,JP11 將 Jumper 裝在 RS422/RS485 端,則使用 RS422/RS485 功能。在選定 RS422/RS485 功能之後,JP5 以及 JP4 若是使用 Jumper 短路,則是 RS485 功能, Jp5 與 JP4 開路,則是使用 RS422 功能,JP6 與 JP7 則是選擇是否適用 120歐母的終端電阻。

# Power: DC 6V 500~900mA

ARNUX7525A 開發板上共有兩種工作電壓 3.3V 和 5V 。ARNUX7525A 開發板外部輸入電壓為 6V ,工作電流約  $500 \sim 900 \text{mA}$  。

# JTAG(Joint Test Action Group):電路介面測試

| Description | Pin | Pin | Description |

|-------------|-----|-----|-------------|

| VDD33       | 1   | 2   | GND         |

| nTRST       | 3   | 4   | GND         |

| TDI         | 5   | 6   | GND         |

| TMS         | 7   | 8   | GND         |

| TCK         | 9   | 10  | GND         |

| TDO         | 11  | 12  | RST1        |

| VDD33       | 13  | 14  | GND         |

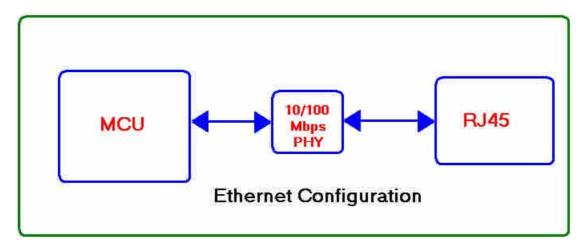

# 乙太網路介面(Ethernet Interface)

ARNUX7525A 開發板具有 10M/100Mbps Ethernet Controller 並使用25MHz 石英震盪器供應 10/100Mbps 乙太網路控制器時序,可自動偵測 10M/100Mbps 的網路環境。以 RJ45乙太網路連接器 方便於連接主電腦或 HUB。

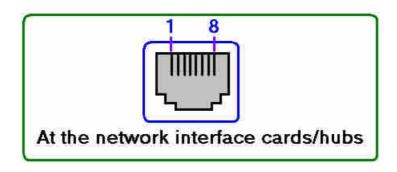

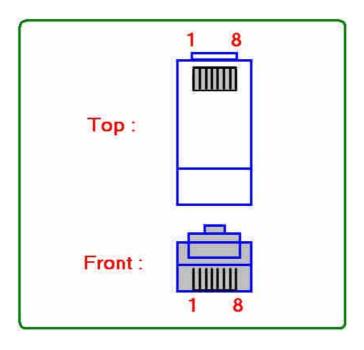

圖1-18. 乙太網路介面(Ethernet Interface) 示意圖

圖1-19. RJ45 公座示意圖

# RJ45 Pin 腳說明 (Connector side)

| Pin Name | Descriptions   |

|----------|----------------|

| 1 TX+    | Transmit Data+ |

| 2 TX-    | Transmit Data- |

| 3 RX+    | Receive Data+  |

| 4 NC     | Not Connected  |

| 5 NC     | Not Connected  |

| 6 RX-    | Receive Data-  |

| 7 NC     | Not Connected  |

| 8 NC     | Not Connected  |

圖1-20 RJ45接腳排列

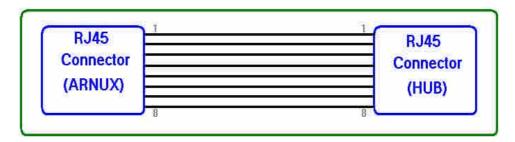

圖1-21 與HUB連接

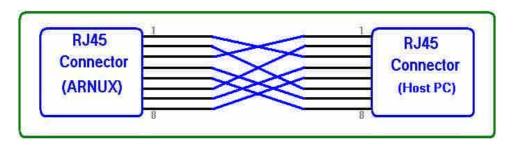

圖1-22 與主電腦連接

# 7.4.RS232 Port Interface

在TxD和RxD:邏輯1(MARK) = -3V  $\sim$  -15V , 邏輯0(SPACE) = +3  $\sim$  + 15V。在RTS、CTS、DSR、DTR和DCD等控制線:信號有效(接通,ON狀態,正電壓)= +3V $\sim$ +15V信號無效(斷開,OFF狀態,負電壓) = -3V $\sim$ -15V 對於資料:邏輯"1"的電壓低於 -3V,邏輯"0"(空號)的電壓高於 +3V;對於控制信號;接通狀態(ON)即信號有效的電壓高於 +3V,斷開狀態(OFF)即信號無效的電壓低於 -3V,也就是當傳輸電壓的絕對值大於3V時,電路可以有效

地檢查出來,介於-3~+3V之間的電壓無意義,低於-15V或高於+15V的電壓也認為無意義,因此,實際工作時,應保證電壓在±(3~15)V之間。

### Com Port Pin 腳說明

| Pin Number | Descriptions |

|------------|--------------|

| 1          | NC           |

| 2          | TxD          |

| 3          | RxD          |

| 4          | DTR          |

| 5          | GND          |

| 6          | DSR          |

| 7          | NC           |

| 8          | NC           |

| 9          | NC           |

# 7.5.RS422/RS485 Port Interface

- A Receiver Input +

- B Receiver Input -

- Z Driver Output -

- Y Driver Output +

# 7.6.CPLD 相關介面

# 7.6.1 LCM

16Pins

| Pin | Description |

|-----|-------------|

| 1   | GND         |

| 2   | VCC         |

| 3   | NC          |

| 4   | RS          |

| 5   | R/W         |

| 6   | Е           |

| 7   | DATA0       |

| 8   | DATA1       |

| 9   | DATA2       |

| 10  | DATA3       |

| 11  | DATA4       |

| 12  | DATA5       |

| 13  | DATA6       |

| 14  | DATA7       |

| 15  | BackLit     |

| 16 | GND |

|----|-----|

|    |     |

20Pins

| Pin | Description |

|-----|-------------|

| 1   | GND         |

| 2   | VCC         |

| 3   | Lit         |

| 4   | RS          |

| 5   | R/W         |

| 6   | Е           |

| 7   | Data0       |

| 8   | Data1       |

| 9   | Data2       |

| 10  | Data3       |

| 11  | Data4       |

| 12  | Data5       |

| 13  | Data6       |

| 14  | Data7       |

| 15  | CS1         |

| 16  | CS2         |

| 17  | RESET#      |

| 18  | NC          |

| 19  | BackLit     |

| 20  | GND         |

7.6.2 Key Pad

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----|----|----|----|----|----|----|----|

| O3 | O2 | 01 | O0 | I3 | I2 | I1 | I0 |

7.6.3 Input / Output

| O12 | O11 | O10 | O9 | O8 | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 |

|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 2   | 4   | 6   | 8  | 10 | 12 | 14 | 16 | 18 | 20 | 22 | 24 | 26 |

| 1   | 3   | 5   | 7  | 9  | 11 | 13 | 15 | 17 | 19 | 21 | 23 | 25 |

| I12 | I11 | I10 | I9 | I8 | I7 | I6 | I5 | I4 | I3 | I2 | I1 | IO |

# IIC BUS

IIC Bus Pin 腳說明:

| Pin Name | Descriptions       |

|----------|--------------------|

| GND      | Ground             |

| SDA      | Serial Clock Input |

| SCL      | Serial Data        |

| VCC      | +5V                |

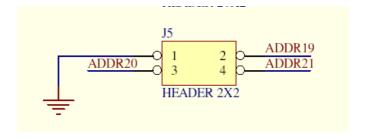

# J5 部分為

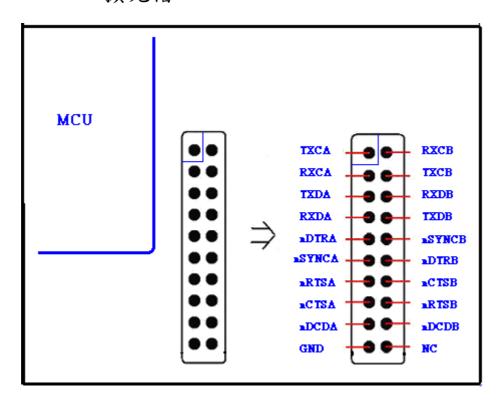

# 7.10 .HDLC 擴充槽

HDLC擴充槽 Pin 腳圖

# HDLC 擴充槽 Pin 腳說明:

| Pin Name  | Type   | Descriptions                                                                                                                                                                       |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDA/TXDB | Output | Ch-A/B Transmit Data. The serial output data from the transmitter is coded in NRZ/NRZI/FM/Manchester data format.                                                                  |

| RXDA/RXDB | Intput | Ch-A/B Receive Data. The serial input data received by the device should be coded in NRZ/NRZI/FM/Manchester data format. The data rate should not exceed the data rate of S3C4510B |

|               |                | internal master clock.                                                                                                                                                                                                                                                                                                                                                      |

|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nDTRA/nDTRB   | Output         | Ch-A/B Data Terminal Ready. NDTRA/NDTRB output indicates that the data terminal device is ready for transmission and reception.                                                                                                                                                                                                                                             |

| nRTSA/nRTSB   | Output         | Ch-A/B Request To Send. The nRTSA/nRTSB output goes low when there is exist data to be sent in TxFIFO. The data to be sent is transmitted when the nCTS is active(Low) state.                                                                                                                                                                                               |

| nCTSA/nCTSB   | Input          | Ch-A/B Clear To Send. The S3C4510B stores each transition of nCTS to ensure that its occurrence would be acknowledged by the system.                                                                                                                                                                                                                                        |

| nDCDA/nDCDB   | Input          | Ch-A/B Data Carrier Detected. A High level on this pin resets and inhibits the receiver register. Data from a previous frame that may remain in the RxFIFO is retained. The S3C4510B stores each transition of nDCD.                                                                                                                                                        |

| nSYNCA/nSYNCB | Output         | Ch-A/B Sync is detected. This indicates the reception of a flag. The nSYNC output goes low for one bit time beginning at the last bit of the flag.                                                                                                                                                                                                                          |

| RXCA/RXCB     | Input          | Ch-A/B Receiver Clock. When this clock input is used as the receiver clock, the receiver samples the data on the positive edge of RXCA/RXCB clock. This clock can be the source clock of the receiver, the baud rate generator, or the DPLL.                                                                                                                                |

| TXCA/TXCB     | Input / Output | Ch-A/B Transmitter Clock. When this clock input is used as the transmitter clock, the transmitter shifts data on the negative transition of the TXCA/TXCB clock. If you do not use TXCA/TXCB as the transmitter clock, you can use it as an output pin for monitoring internal clocks such as the transmitter clock, receiver clock, and baud rate generator output clocks. |