# 嵌入式系统原理与设计

徐 端 全 华中科技大学电子与信息工程系

# 第一章 嵌入式系统概述

# 1.1 什么是嵌入式系统

#### 1.1.1 计算机的基本概念

嵌入式系统(Embedded system)也称嵌入式计算机系统。顾名思义,嵌入式系统是计算机的一种特殊形式,所以在理解嵌入式系统概念前,必须先明确计算机的基本概念。

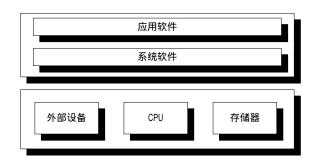

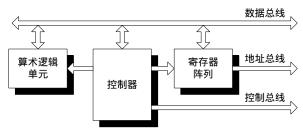

计算机是能按照指令对各种数据进行自动加工处理的电子设备,一套完整的计算机系统包括硬件和软件两个部分。软件是指令与数据的集合,而硬件则是执行指令和处理数据的环境平台,是那些看得见、摸得着的部件。计算机的硬件系统主要由中央处理器(CPU)存储器、外部设备以及连接各个部分的计算机总线组成。

图 1.1 计算机系统的组成

自 1946 年第一台电子计算机问世以来,计算机技术发展迅猛,经历了电子管计算机、 晶体管计算机、小规模集成电路计算机和大规模集成电路计算机四个阶段。

现在为人所熟知的台式机、便携机等性能强大,安装不同的软件就能实现不同的功能, 其应用并不局限于特定的领域,如果安装了专门的软件开发工具,它就是一台软件开发计 算机;如果安装了办公软件,它就是一台办公计算机;如果安装了游戏软件,它就是一台 游戏机.....

随着计算机技术的发展,计算机应用越来越广泛,大量的设备需要采用计算机技术实现数据采集、自动控制、信息处理的功能,而这种应用中的计算机是专用的、是整个设备或系统的固定组成部分。这就是我们所说的嵌入式系统。

#### 1.1.2 嵌入式系统定义

嵌入式系统是以应用为中心、计算机技术为基础,软、硬件可剪裁,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

上述定义较好地描述了嵌入式系统各方面的特征,不同的应用对计算机的有不同的需求,嵌入式计算机在满足应用对功能和性能需求的前提下,还要适应应用对计算机的可靠性、机械结构、功耗、环境适应性等方面的要求,在一般情况下,还要尽量降低系统的成本。

简单地说,嵌入式系统是为具体应用定制的专用计算机系统,定制过程既体现在软件方面,也体现在硬件方面。硬件上,针对应用,选择适当的芯片、体系结构,设计满足应用需求的接口、设计方便安装的机械结构:软件上则明确是否需要操作系统、配置适当的

系统软件环境、编写专门的应用软件。

#### 1.2 嵌入式系统与通用计算机系统

根据用途可以把计算机分成两大类:通用计算机和嵌入式计算机。嵌入式计算机是针对特定的应用进行专门设计的,发展方向是提高嵌入性能、提高控制能力和控制的可靠性;而通用计算机则不同,其硬件功能全面,而且具有较强的扩充能力,软件上配置标准操作系统及其它常用系统软件与应用软件,发展方向是计算速度的无限提升、总线带宽的无限扩展、存储容量的无限扩大。

都是计算机,嵌入式系统与通用计算机系统基本原理上没有什么根本的不同,但因为应用目标不一样,嵌入式系统有着自身的特点:

1) 嵌入式系统具有应用针对性。

这是嵌入式系统的一个基本特征,体现这种应用针对性的首先是软件,软件实现特定应用所需要的功能,所以嵌入式系统应用中必定配置了专用的应用程序;其次是硬件,大多数嵌入式系统的硬件是针对应用专门设计的,但也有一些标准化的嵌入式硬件模块,采用标准模块降低开发的技术难度和风险,缩短开发时间,但灵活性不足。

2) 嵌入式系统硬件一般对扩展能力要求不高。

硬件上,作为一种专用的计算机系统,功能、机械结构、安装要求比较固定,所以嵌入式系统一般没有或仅有较少的扩展能力;软件上,嵌入式系统往往是一个设备固定组成部分,其软件功能由设备的需求决定,在相对较长的生命周期里,一般不需要对软件进行改动。但也有一些特例,比如现在的手机,尤其是安装有嵌入式操作系统的智能手机,软件安装、升级比较灵活,但相对桌面计算机其软件扩展能力还是相当弱。

3) 嵌入式系统一般采用专门针对嵌入式应用设计的中央处理器。

这与嵌入式系统应用针对性有关,相对通用计算机处理器,嵌入式处理器种类繁多,不同的嵌入式处理器功能/性能差异非常大,主频从几兆赫兹到千兆赫兹、引脚数量从几个到几百个,只有这种多样化才能适应千差万别的嵌入式系统应用。

4) 嵌入式系统中操作系统可能有也可能没有,且嵌入式操作系统与桌面计算机操作系统有较大差别。

在现代的通用计算机中,没有操作系统是无法想象的,而在嵌入式计算机中情况则大不相同。在一个功能简单的嵌入式系统中,可能根本不需要操作系统,直接在硬件平台上运行应用程序;而一些功能复杂的嵌入式系统,可能需要支持有线/无线网络、文件系统、实现灵活的多媒体功能、支持实时多任务处理,此时,在硬件平台和应用软件之间增加一个操作系统层,可使应用软件的设计变得简单,而且便于实现更高的可靠性,缩短系统开发时间,使系统的研发工作变得可控。

目前存在很多种嵌入式操作系统,如 VxWorks、pSOS、嵌入式 Linux、WinCE 等,这些操作系统功能日益完善,以前只在桌面通用操作系统具备的功能,如网络浏览器、HTTP服务器、Word 文档阅读与编辑等,也可以在嵌入式系统中实现。但为适应嵌入式系统的需要,嵌入式操作系统相对通用操作系统,具有模块化、结构精练、定制能力强、可靠性高、实时性好、便于写入非易失性存储器(固化)等特点。

5) 嵌入式系统一般有实时性要求。

设备中的嵌入式系统常用于实现数据采集、信息处理、实时控制等功能,而采集、处理、控制往往是一个连续的过程。一个过程要求必须在一定长的时间内完成,这就系统实时性的要求。

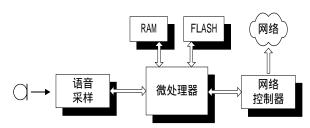

如在图 1.3 所示的语音处理系统中,实现实时的数据采集、编码、并通过网络传输的

功能。按照 8kHZ 采样率、精度 8bits 的工作模式进行单通道语音采样,这时系统会以每秒 8kB 的速率连续产生数据,计算机需要"及时"地进行语音数据采集、数据压缩编码、通过网络把数据发送出去这些处理,任何一个环节处理不及时,都会导致语音数据丢失。

图 1.2 语音处理系统结构图

实时性和处理器速度不是一回事,速度快的系统不一定实时性好,速度慢的系统实时性未必不能满足要求。计算机运行速度高,当然更有条件实现实时性,但不是实时性的充要条件。嵌入式系统的设计要求精练,因此在运算速度上不会留太多余量,为了保证实时性要求,更需要对硬件、软件精心设计。

6) 嵌入式系统一般有较高的成本控制要求。

在满足需求的前提下,在嵌入式系统开发中,要求高效率地设计,减少硬件、软件冗余,恰到好处的设计可以最大限度地降低系统成本,并有利于提高系统的可靠性。

通用计算机则追求更快的计算速度、更大的存储容量、更丰富的配置、更大的显示器。 强大的硬件平台才能满足日益复杂的桌面操作系统及各种类型软件的需要,这样的计算机"通用性"才最强。

7) 嵌入式系统软件一般有固化的要求。

在现代的通用计算机中,硬盘是操作系统和应用软件的载体,对于这些几 GB, 甚至 几十 GB、几百 GB 的软件及数据,硬盘是最好的记录媒介。

嵌入式系统软件一般把操作系统和应用软件直接固化在非易失性存储器(如 FLASH存储器)中。首先,嵌入式系统一般没有硬盘,就算有硬盘或存储卡之类的外部存储器,也很少用于存储系统软件,多是用于存储数据或用户扩展的软件;其次,无论是操作系统还是应用软件都很精练,所占容量相对通用计算机要小得多,所以有固化的条件;再次,嵌入式系统不象通用计算机那么容易安装和升级软件,而且也很少需要改动,所以要求软件存储可靠性高,因此有必要把软件固化;最后,软件固化有利于提高嵌入式系统的启动速度。

8) 嵌入式系统软件一般采用交叉开发的模式。

目前软件设计工作大多采用集成开发环境,将代码编辑、编译、链接、仿真、调试等软件开发工具集成在一起。嵌入式系统针对具体的应用进行设计,其硬件、软件的配置往往不便于或不可能支持应用软件开发。实际开发中,一般用通用计算机(主要是 PC 机)作为开发机,进行嵌入式软件的编辑、编译、链接,在开发机上进行仿真,或下载到嵌入式目标系统是运行测试,最终的目标代码固化到目的系统的存储器中运行,这就是所谓交叉开发的软件设计模式。

9) 嵌入式系统在体积、功耗、可靠性、环境适应性上一般有特殊要求

嵌入式系统作为一个固定的组成部分"嵌入"在设备中,因受装配、供电、散热等条件的约束,其体积、功耗必然有一定的限制。例如,现在的手机功能日益强大,但体积越做越小,集成度和装配密度非常高,在这种应用环境里,嵌入式计算机部分的芯片封装、

电路板设计、系统装配等都要求紧凑、小巧。在功耗方面也有严格的要求,一方面密封在 手机里,没有良好的散热条件,功耗控制不好会导致手机温度过高;另一方面,电路的功 耗直接决定了手机一次充电后持续工作的时间。

嵌入式系统作为设备的核心,其可靠性直接决定了设备可靠性,因此在这方面有严格的要求。尤其在航空、航天、武器装备等应用中,嵌入式系统的可靠性更是生死悠关的事情。

# 10) 嵌入式系统技术标准化程度不高。

PC 是最普及的通用计算机,其主板结构、计算机扩展总线、扩展板结构、内存扩展、电源、机箱、外部设备接口,甚至安装螺钉等都完全标准化,所以 PC 机完全以社会化分工的形式进行批量大规模生产。PC 的标准化不仅体现在硬件上,软件上也有很高的标准化趋势,如数据库标准、操作系统标准、文本标准等等。

每个嵌入式系统都是针对具体应用设计,所以千差万别,不可能象 PC 一样制定高度一致的标准,也正是因为这个原因,在嵌入式领域才不会形成个别企业垄断市场的现象。

标准化有利于社会化的分工合作,嵌入式领域也存在一定程度的标准化,如 PC104 总线标准、Compact PCI 总线标准等,只是这些标准的应用相对于整个嵌入式领域还是很小的一部分。

嵌入式系统与通用计算机系统技术上是相通的,通用计算机发展快、性能强,很多技术可以应用到嵌入式系统中,如 PC 中的 ISA 总线经过改造成为嵌入式系统中的 PC104 总线、PCI 总线经过改造成为嵌入式系统中的 CompactPCI 总线;桌面 Windows XP 操作系统有对应的嵌入式版本——Windows XP Embedded,而桌面 Linux 也有对应的嵌入式 Linux 版本。在应用中,还经常可见经过机械结构、环境适应性改造的通用计算机应用在嵌入式领域中。

#### 1.3 嵌入式系统的发展与应用

如果问哪种计算机最普及,有人会说是 PC 机,可实际上嵌入式系统在数量上远远超过了以 PC 机为代表的通用计算机,只是嵌入式系统一般集成在设备内部,不象 PC 那样本身是一个独立的系统,配备显示器、键盘、鼠标等标准设备。

人们在使用设备时,往往在意的是设备提供的功能,而忽略了在设备内部高速运转、起着核心作用的嵌入式系统,例如在用 MP3 欣赏音乐的时候,人们只关心音乐的音质、操控方式、系统容量、支持的音乐格式等,有多少人会关心在 MP3 内部发挥作用的嵌入式计算机呢?可实际上所有的功能都是内部的计算机完成的。

早期计算机由电子管组成,体积庞大,主要用于完成复杂的计算任务。随着晶体管计算机的出现,尤其是集成电路在计算机中的应用,计算机体积越来越小、性能越来越强,除了数值计算外,计算机还可以实现数据采集、信息处理、自动控制等功能,将专门设计的计算机集成到传统设备中,可显著提高设备的性能。此时,一种新的计算机类型——嵌入式系统应运而生。

嵌入式系统发展之初,因为计算机还是个昂贵的电子设备,所以应用仅限于军事、工业控制等成本不敏感的领域。随着微处理器技术的飞速发展,计算机集成度越来越高,在性能提高的同时,计算机也变得越来越小、越来越廉价,嵌入式系统的进入蓬勃发展时期。

现代社会生活中,嵌入式系统无处不在,广泛应用在国防电子、数字家庭、工业自动化、汽车电子、医学科技、消费电子、无线通讯、电力系统等各行各业。嵌入式系统是数字化社会的技术基础,正如中科院院士沈绪榜教授所说,"计算机是认识世界的工具,而嵌入式系统则是改造世界的产物。"

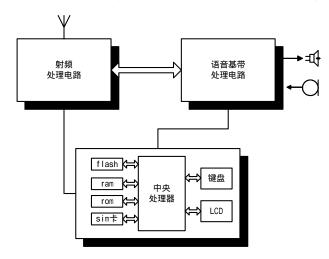

图 2 给出的是数字手机电路的原理框图,嵌入式系统在手机里完成人机接口、信息管理、设备控制等功能,在多媒体手机中,嵌入式系统还要实现语音记录、视频记录、数码相机、音视频文件播放等多媒体功能。嵌入式系统是数字手机的核心。

图 1.3 手机电路原理框图

现代社会日益数字化、信息化,嵌入式系统在这样的社会中必将扮演重要的角色。如在日常生活中,将来嵌入式系统不仅存在于电视机、洗衣机、冰箱、洗衣机、手机这些设备里,甚至我们穿的鞋子、戴的帽子、穿的衣服中也装备了计算机系统。

1999 年, IBM 提出了普适计算的概念, 指得是随时随地获取信息、处理信息。普适计算涉及移动通信技术、小型计算机设备制造技术、小型计算机设备上的操作系统技术及软件技术等。嵌入式系统是实现普适计算的基础技术之一。

# 1.4 嵌入式系统的组成

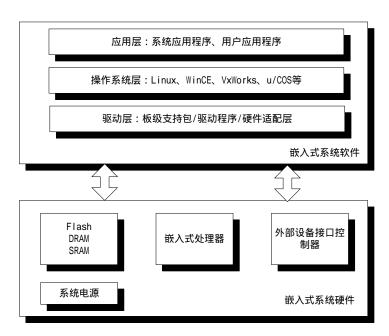

嵌入式系统是具有应用针对性的专用计算机系统,应用时作为一个固定的组成部分"嵌入"在应用对象中。每个嵌入式系统都是针对特定应用定制的,所以彼此间在功能、性能、体系结构、外观等方面可能存在很大的差异,但从计算机原理的角度看,嵌入式系统包括硬件和软件两个组成部分。

图 1.4 给出的是一个典型的嵌入式系统组成,实际系统中可能并不包括所有的组成部分。

嵌入式系统硬件部分以嵌入式处理器为核心,扩展存储器及外部设备控制器。在某些应用中,为提高系统性能,还可能为处理器扩展 DSP 或 FPGA 等作为协处理器,实现视频编码、语音编码及其它数字信号处理等功能。在一些 SOC(System On Chip)中,将 DSP或 FPGA 与处理器集成在一个芯片内,降低系统成本、缩小电路板面积、提高系统可靠性。

嵌入式系统软件部分,驱动层向下管理硬件资源,向上为操作系统提供一个抽象的虚拟硬件平台,是操作系统支持多硬件平台的关键。在嵌入式系统软件开发过程中,用户的主要精力一般在用户应用程序和设备驱动程序开发上。

图 1.4 嵌入式系统组成

# 1.5 嵌入式系统的分类

嵌入式系统种类繁多,应用在各行各业里,对其分类有很多不同的方法。

#### 1.5.1 按处理器位宽分类

按处理器位宽可将嵌入式系统分为 4 位、8 位、16 位、32 位系统,一般情况下,位宽越大,性能越强。

对于通用计算机处理器,因为要追求尽可能高的性能,在发展历程中总是高位宽处理器取代、淘汰低位宽处理器。而嵌入式处理器不同,千差万别的应用对处理器要求也大不相同,因此不同性能处理器都有各自的用武之地。

#### 1.5.2 按有无操作系统分类

现代通用计算机中,操作系统是比不可少的系统软件。在嵌入式系统中则有两种情况:有操作系统的嵌入式系统和无操作系统(裸机)的嵌入式系统。

在有操作系统支持的情况下,嵌入式系统的任务管理、内存管理、设备管理、文件管理等都由操作系统完成,并且操作系统为应用软件提供丰富的编程接口,用户应用软件开发可以把精力都放在具体的应用设计上,这与在 PC 上开发软件相似。

在一些功能单一的嵌入式系统中,如基于8051单片机嵌入式系统,硬件平台很简单,系统不需要支持复杂的显示、通信协议、文件系统、多任务的管理等,这种情况下可以不用操作系统。

#### 1.5.3 按实时性分类

根据实时性要求,可将嵌入式系统分为软实时系统和硬实时系统两类。

在硬实时系统中,系统要确保在最坏情况下的服务时间,即对事件响应时间的截止期限必须得到满足。在这样的系统里,如果一个事件在规定期限内不能得到及时处理则会导

#### 致致命的系统错误。

在软实时系统中,从统计的角度看,一个任务能够得到确保的处理时间,到达系统的时间也能够在截止期限前得到处理,但截止期限条件没得到满足时并不会带来致命的系统错误。

#### 1.5.4 按应用分类

嵌入式系统应用在各行各业,按照应用领域的不同可对嵌入式系统进行分类。

# 1) 消费类电子产品

消费类电子产品是嵌入式系统需求最大的应用领域,日常生活中的各种电子产品都有嵌入式系统的身影,从传统的电视、冰箱、洗衣机、微波炉,到数字时代的影碟机、MP3、MP4、手机、数码相机、数码摄像机等,在可预见的将来,可穿戴计算机也将走入我们的生活。现代社会里,人们被各种嵌入式系统的应用产品包围着,嵌入式系统已经在很大程度上改变了我们的生活方式。

# 2) 过程控制类产品

这一类的应用有很多,如生产过程控制、数控机床、汽车电子、电梯控制等等。过程 控制引入嵌入式系统可显著提高效率和精确性。

#### 3) 信息、通信类产品

通信是信息社会的基础,其中最重要的是各种有线、无线网络,在这个领域大量应用 嵌入式系统,如路由器、交换机、调制解调器、多媒体网关、计费器等。

很多与通信相关的信息终端也大量采用嵌入式技术,如 POS 机、ATM 自动取款机等。使用嵌入式技术的信息类产品还包括键盘、显示器、打印机、扫描仪等计算机外部设备。

# 4) 智能仪器、仪表产品

嵌入式系统在智能仪器、仪表大量应用,采用计算机技术不仅提高仪器、仪表性能,还可以设计出传统模拟设备所不具备的功能。如传统的模拟示波器能显示波形,通过刻度人为计算频率、幅度等参数,而基于嵌入式计算机技术设计的数字示波器,除更稳定显示波形外,还能自动测量频率、幅度,甚至可以将一段时间里的波形存储起来,供事后详细分析。

# 5) 航空、航天设备与武器系统

航空、航天设备与武器系统一向是高精尖技术集中应用的领域,如飞机、宇宙飞船、卫星、军舰、坦克、火箭、雷达、导弹、智能炮弹等等,嵌入式计算机系统是这些设备的 关键组成部分。

#### 6) 公共管理与安全产品

这类应用包括智能交通、视频监控、安全检查、防火防盗设备等。饿现在常见的可视 安全监控系统已基本实现数字化,在这种系统中,嵌入式系统常用于实现数字视频的压缩 编码、硬盘存储、网络传输等,在更智能的视频监控系统中,嵌入式系统甚至能实现人脸 识别、目标跟踪、动作识别、可疑行为判断等高级功能。

#### 7) 生物、医学微电子产品

这类应用包括生物特征(指纹、虹膜)识别产品、红外温度检测、电子血压计、一些电子化的医学化验设备、医学检查设备等。

# 第二章 嵌入式处理器

# 2.1 处理器原理 (*RISC CISC 哈佛 冯*)

处理器,即中央处理器 ( CPU ),是所有计算机的核心,在理解嵌入式处理器前,不妨先回顾一下处理器的原理。

#### 2.1.1 CPU 的指令系统

指令是 CPU 能理解并执行的命令单元,一条完整的指令一般包括操作码和操作数两个部分,操作码决定要完成的操作,而操作数则是操作过程中需要的数据或数据的地址。

现代 CPU 都采用二进制表达方法,计算机硬件只识别"0"和"1"两个数字,所有的 CPU 指令都由这两个数字进行编码。例如某个指令系统的指令长度为 32 位,操作码长为 8 位,地址码长度也为 8 位,当收到一个"0000010 00000100 00000001 00000110"的指令时,先分析前面的 8 位操作码,判断为减法操作,后面是三个操作数地址,CPU 在00000100 地址中取出被减数,在 00000001 地址取出减数,送到 CPU 的算术逻辑单元中进行减法运算,并将计算结果送到 00000110 地址中。

一条指令只能完成一个简单的功能,如加/减运算、逻辑判断、读数据、写数据等,如果要完成复杂功能,就需要把很多很多指令组合起来协调执行,这些有机组合在一起的一串指令就是程序。

不同 CPU 支持的指令不同, CPU 支持的所有指令的集合就是该 CPU 的指令系统,如 x86 指令系统、ARM 指令系统、MCS-51 指令系统等。指令系统是 CPU 的基本属性。

指令系统主要包括以下几种类型的指令:

1) 算术运算指令

主要包括加、减、乘、除等数的计算。

2) 逻辑运算指令

实现逻辑数的与、或、非、异或等逻辑运算。

3) 数据传送指令

实现寄存器与寄存器、寄存器与存储单元以及存储单元与存储单元之间数据的传送。

4) 移位操作指令

包括算术移位、逻辑移位和循环移位三种,实现对操作数左移、右移一位或若干位。

5) 其它指令

除以上指令外还有一些其它指令,如堆栈操作指令、转移类指令、输入输出指令、多处理器控制指令、空操作指令等。

#### 2.1.2 CPU 的分类

根据结构不同,可把处理器分为哈佛结构处理器和冯·诺依曼结构处理器。

在冯·诺伊曼结构处理器中,程序指令和数据采用统一的存储器,对数据和指令的寻址不能同时进行,只能交替完成。

有别于冯·诺伊曼结构,在哈佛结构的处理器中,数据和指令分开存储,通过不同的总线访问,具体特点体现在两个方面:

- 程序存储器和数据存储器分离,分开存储指令和数据

- 使用两套彼此独立的存储器总线 , CPU 通过两套总线分别读、写程序存储器或数据存储器

哈佛结构的处理器中,因为有两套相互独立的指令和数据存储器总线,因此可以同时

进行指令和数据的访问,从而提高系统性能。而改进的哈佛结构处理器中,独立的存储总 线可以不只两套,比如有多套数据存储器总线,可以进一步提高数据访问的速度。

根据指令格式的不同可以把 CPU 分为 CISC ( Complex Instruction Set Computer,复杂指令集计算机)处理器和 RISC ( Reduced Instruction Set Computer,精简指令集计算机)处理器。

早期的 CPU 都采用 CISC 指令,最典型的就是 x86 系列处理器。CISC 的特点是有大量复杂的指令、指令长度可变、寻址方式多样。

在计算机发展之初,CPU 指令系统包含很少的指令,一些复杂的操作通过简单指令的组合来实现,如两个数 a 和 b 相乘可以用 a 个 b 的加法来实现。随着集成电路技术的迅速发展,为了软件编程方便和提高程序运行速度,在 CPU 的设计中不断增加可实现复杂功能的指令,如乘法运算中直接使用乘法指令而不是多个数的累加。随着复杂指令增多,CPU 指令系统变得越来越复杂。

指令越来越多、越来越复杂带来另一个问题,因为指令系统的指令数量由指令操作码的位数决定。如指令数量为n,指令码位数为k,则 $n=2^k$ 。CPU 指令编码宽度不可能随意增加,促使操作码扩展技术出现。假如操作码为 2 位,则正常情况可表示四个指令,分别是 00、01、10、11。为了增加指令长度,如果把编码"11"作为扩展码,并把操作码扩展到 4 位,则该指令系统就有 00、01、10、1100、1101、1110、1111等七条指令,这就是长度可变的操作码编码方式。

上述这种具有大量复杂指令、指令长度可变、且寻址方式多样的指令系统就是传统 CISC 指令系统。

采用复杂指令系统的计算机有着较强的处理高级语言的能力,这有益于提高计算机的性能,但另一方面,复杂的指令、变长的编码、灵活的寻址方式大大增加了指令解码的难度,而在现在的高速硬件发展下,复杂指令所带来的速度提升已不及在解码上浪费点的时间。

IBM 公司于 1975 年组织力量研究指令系统的合理性问题,发现 CISC 存在的一些缺点:首先,在这种计算机中,各种指令的使用率差别很大,一个典型程序的运算过程所使用的 80%指令,只占一个处理器指令系统的 20%,最频繁使用的是取、存和加这些最简单的指令,而占指令数 80%的复杂指令却只有 20%的机会用到。复杂的指令系统必然带来结构的复杂性,增加了设计、制造的难度,尽管大规模集成电路技术已达发展到很高的水平,但也很难把 CISC 的全部硬件做在一个芯片上,妨碍单片计算机的发展;另外,在 CISC中,许多复杂指令需要完成复杂的操作,这类指令多数是某种高级语言的直接翻版,因而通用性差,采用二级的微码执行方式,降低了那些被频繁调用的简单指令系统的运行速度。

针对 CISC 的这些弊病,业界提出了精简指令的设计思想,即指令系统应当只包含那些使用频率很高的少量指令,并提供一些必要的指令以支持操作系统和高级语言,按照这个原则发展而成的计算机被称为精简指令集计算机(Reduced Instruction Set Computer-RISC)结构,简称 RISC。

RISC 的最大特点是指令长度固定,指令种类少,寻址方式种类少,大多数是简单指令且都能在一个时钟周期内完成,易于设计超标量与流水线,寄存器数量多,大量操作在寄存器之间进行。一般认为 RISC 处理器有以下几个方面的优点:

#### 1) 芯片面积小

实现精简的指令系统需要的晶体管少,芯片面积自然就小一些。节约的面积可以用于实现提高性能的功能部件,如高速缓存、存储器管理和浮点运算器等,也便于在单片上集成更多其它模块,如网络控制器、语音/视频编码器、SDRAM 控制器、PCI 总线控制器等。

#### 2) 开发时间短

开发一个结构简洁的处理器在人力、物力上的投入要更少,整个开发工作的开发时间 更易于预测可控制。

# 3) 性能高

在 CISC 处理器中,一些复杂的操作有专用的指令,对于单个的操作使用专用指令可以提高处理效率,但复杂指令的使用降低了所有其它指令的执行效率。完成同样功能的程序时,RISC 处理器需要更多的指令,但 RISC 单个指令执行效率高,而且 RISC 处理器容易实现更高的工作频率,从来使整体性能得到提高。RISC 处理器的性能上的优点在处理器发展的实践中得到验证。

目前,通用计算机,如个人电脑、服务器等大多采用 CISC 结构的 x86 处理器,随着技术的发展,新的 x86 处理器融合了 RISC 的特性。在嵌入式处理器中,RISC 技术则得到普遍的应用,如 MIPS 处理器、ARM 处理器等。

# 2.1.3 CPU 结构 (分两类: 冯 哈佛)

CPU 典型组成部分包括运算器、控制器、寄存器阵列及连接各个部分的内部总线,如图 2.1 所示。

运算器包括算术逻辑单元、累加器、暂存器及标志寄存器等,完成加、减、乘、除四则运算及各种逻辑运算。

控制器由指令寄存器、指令译码器、控制逻辑电路组成,完成 CPU 的全部控制功能。 CPU 从存储器取出指令,通过数据总线存入指令寄存器,然后由指令译码器对指令进行译码。译码产生的结果与时钟信号配合,在控制逻辑电路中产生各种操作所必须的控制信号。 控制信号经由控制总线送到微处理器系统的其它功能部件中,以便执行各种操作。

CPU 在操作过程中需要获取数据并产生一些新数据,为了提高 CPU 的速度,在 CPU 内部设计一组临时存储器单元,用于操作数据及中间结果的存放与转移,这就是 CPU 的寄存器阵列。

图 2.1 CPU 内部结构

上面描述的只是 CPU 的最基本组成,现在一般意义的 CPU 内部包含的内容比这要丰富得多,如可能集成了 cache(高速缓存),中断控制器、动态 RAM 控制器、PCI 总线控制器等,甚至一个芯片内集成了多个处理器核。

# 2.1.4 Big endian 和 Little endian

在计算机中,内存可寻址的最小存储单位是字节。多字节数存放在内存时存在字节顺序的问题,既高位字节在前,还是低位字节在前?不同的处理器采取的字节顺序可能不一样, Motorola 的 PowerPC 系列 CPU 和 Intel 的 x86 系列 CPU 是两个不同字节顺序的典型代表。PowerPC 系列中低地址存放最高有效字节,既所谓用 Big endian 方式;x86 系列中

则低地址存放最低有效字节,既所谓 Little endian 方式。

图 2.2 更清楚地说明 Big endian 和 Little endian 的区别。对于一个 16 进制 4 字节数 0x12345678,其最高有效字节是 0x12,最低有效字节是 0x78,存储的起始地址是 0。 Big endian 存储方式里,最高有效字节是 0x12 存放在最低地址处,而 Little endian 存储方式里最低地址处存放的是最低有效字节 0x78。

嵌入式系统开发中,字节序的差异可能带来软件兼容性问题,需要特别注意。在很多嵌入式处理中, Big endian 和 Little endian 两种模式都可以支持,需要对处理器设置相应工作模式。

| 字节地址 | 00   | 01   | 02   | 03   |

|------|------|------|------|------|

| 字节   | 0x12 | 0x34 | 0x56 | 0x78 |

(a) Big endian 字节序的字节存储方式

| 字节地址 | 00   | 01   | 02   | 03   |

|------|------|------|------|------|

| 字节   | 0x78 | 0x56 | 0x34 | 0x12 |

(a) Big endian 字节序的字节存储方式 图 2.2 不同字节序的多字节数存储方式

#### 2.1.5 影响 CPU 性能的因素

影响 CPU 性能的因素有很多,主要有以下几种:

- 1) CPU 的字长,也就是 CPU 内部总线的宽度,字长有4位、8位、16位、32位、64位等类型,一般字长越大,性能越强

- 2) 指令效率与单指令执行所需要的时间

- 3) CPU 的系统架构,

#### 2.2 嵌入式处理器分类

参照通用计算机与嵌入式系统的分类,可以将微处理器分为通用处理器与嵌入式处理器两类。

通用处理器以 x86 体系结构的产品为代表,基本为 Intel 和 AMD 两家公司所垄断。通用处理器针对通用计算机的需要进行设计,追求更快的计算速度、更大的数据吞吐率,从8 位、16 位、32 位、到 64 位一代代发展过来。通用处理器也可能应用在一些需要很高计算性能的嵌入式系统中,如在一些 PC104、Compact PCI 的主控板上可见到 Celoron、Pentium处理器,这是通用计算机技术在嵌入式领域的一种应用。

在整个嵌入式领域,通用处理器的应用只是凤毛麟角,真正的主角当然是各色嵌入式处理器。因为嵌入式系统有应用针对性的特点,不同的系统对处理器要求千差万别,所以嵌入式处理器种类繁多,据不完全统计,全世界嵌入式处理器的种类已经超过 1000 种,流行的体系结构有 30 多个。

所有嵌入式处理器中,8051 体系的占有多半,生产8051 单片机的半导体厂家有20多个,共350多种衍生产品。现在几乎每个半导体制造商都生产嵌入式处理器,越来越多的公司有自己的处理器设计部门。

嵌入式系统中的处理器可以分成下面几类。

嵌入式微处理器 ( Micro Processor Unit , MPU )

嵌入式微处理器字长一般为 16 位或 32 位, Intel、AMD、Motorola、ARM 等公司提供很多这样的处理器产品。嵌入式微处理器通用性比较好、处理能力较强、可扩展性好、寻址范围大、支持各种灵活的设计,且不限于某个具体的应用领域。

在应用中,嵌入式微处理器需要在芯片外配置 RAM 和 ROM,根据应用要求往往要扩展一些外部接口设备,如网络接口、GPS、A/D 接口等。嵌入式微处理器及其存储器、总线、外设等安装在一块电路板上,称之为单板计算机。

嵌入式微处理器在通用性上有点类似通用处理器,但前者在功能、价格、功耗、芯片 封装、温度适应性、电磁兼容方面更适合嵌入式系统应用要求。

嵌入式处理器有很多种类型,如 xScale、Geode、Power PC、MIPS、ARM 等处理器系列。

# ● 嵌入式微控制器 (Microcontroller Unit, MCU)

嵌入式微控制器又称单片机,已经经历了近 30 年的发展历史,目前在嵌入式系统中仍然有着极其广泛的应用。这种处理器内部集成 RAM、各种非易失性存储器、总线控制器、定时/计数器、看门狗、I/O、串行口、脉宽调制输出、A/D、D/A 等各种必要功能和外设。和嵌入式微处理器相比,微控制器的最大特点是将计算机最小系统所需要的部件及一些应用需要的控制器/外部设备集成在一个芯片上,实现单片化,使得芯片尺寸大大减小,从而使系统总功耗和成本下降、可靠性提高。微控制器的片上外设资源一般比较丰富,适合于控制,因此称微控制器。 MCU 品种丰富、价格低廉,目前占嵌入式系统约 70%以上的市场份额。

● 嵌入式 DSP (Embedded Digital Signal Processor, EDSP)

在数字化时代数字信号处理是一门应用广泛的技术,如数字滤波、FFT、谱分析、语音编码、视频编码等、数据编码、雷达目标提取等等,传统微处理器在进行这类计算操作时的性能较低,专门的数字信号处理芯片——DSP 也就应运而生,DSP 的系统结构和指令系统针对数字信号处理进行了特殊设计,因而在执行相关操作时具有很高的效率。

在应用中, DSP 总是完成某些特定的任务, 硬件和软件需要为应用进行专门定制, 因此 DSP 是一种嵌入式处理器。

嵌入式片上系统(System On Chip, SOC)

某一类特定的应用对嵌入式系统的性能、功能、接口有相似的要求,针对嵌入式系统的这个特点,利用大规模集成电路技术将某一类应用需要的大多数模块集成在一个芯片上,从而在芯片上实现一个嵌入式系统大部分核心功能,这种处理器就是 SOC。

SOC 把微处理器和特定应用中常用的模块集成在一个芯片上,应用时往往只需要在 SOC 外部扩充内存、接口驱动、一些分立元件及供电电路就可以构成一套实用的系统,极 大地简化了系统设计的难度,同时还有利于减小电路板面积、降低系统成本、提高系统可靠性。SOC 是嵌入式处理器的一个重要发展趋势。

嵌入式微控制器和 SOC 都具有高集成度的特点,将计算机小系统的全部或大部分集成在单个芯片中,有些文献将嵌入式微控制器归为 SOC。本书为了更清晰地描述,将内部集成了 RAM 和 ROM 存储器、主要用于控制的单片机称为微控制器,而所说的 SOC 则没有内置的存储器,以嵌入式微处理器为核心、集成各种应用需要的外部设备控制器,具有较强的计算性能。

# 2.3 嵌入式处理器特点

嵌入式处理器针对嵌入式系统特殊需要设计,相对通用处理器具有以下特点:

1) 嵌入式处理器种类繁多、功能多样、性能跨度大

这是由嵌入式系统应用针对性决定的。不同的系统对处理器的功能、性能、功耗、工作环境、封装等要求不同,适应千奇百怪的应用需要,嵌入式处理器发展出极其丰富的产品类型。这与通用处理器有很大的区别,应用在通用计算机的处理器产品追求的是高性能,接口和功能有一定的标准规范,流行的产品种类有限。

#### 2) 嵌入式处理器功耗低

嵌入式系统往往作为一个部件"嵌入"在一个设备/系统中,因供电限制或散热的限制,功耗必须得到有效控制。在嵌入式系统中处理器往往是功耗最大的器件,所以嵌入式处理器一般都有良好的功耗设计,尤其在电池供电的系统中,功耗是个至关重要的问题。

# 3) 提供灵活的地址空间寻址能力

通用计算机结构标准化程度高,其地址空间的划分很明确。但嵌入式系统则不同,因为嵌入式应用千差万别,嵌入式系统地址空间的分配有很大的自由度,为了适应嵌入式系统的这个特点,嵌入式处理器一般有灵活的地址空间寻址能力。为此,一些嵌入式处理器提供多个片选信号,而且片选信号对应的起始地址、存储空间范围、存储器位宽可以自由设置。

## 4) 支持灵活的功耗控制

嵌入式处理器一般有严格的功耗设计,除了降低正常工作的功耗外,还有很多降低功耗的措施,如可变工作频率、降低工作电压,还可以设置多种工作模式,如正常模式、睡眠(Sleep)模式、下电(Power down)模式等

#### 5) 功能密集,提供丰富的外部接口

为了降低功耗、降低系统成本、使系统更精简,嵌入式处理器中功能模块的集成度越来越高,除了处理器核心外,很多的传统的外部控制器被集成到微处理器中,如中断控制器、LCD 显示控制器、串行接口控制器、USB 控制器、网络控制器等等。

# 2.48051 单片机原理

从 1980 年开始, Intel 公司陆续推出了 MCS-51 单片机系列, 8051 是其中的第一个型号,该单片机因先进的硬件设计和高效的指令系统而得到广泛的认同。Intel 除了自己生产多种型号的 MCS-51 单片机外,还将该处理器内核技术授权给其他公司,如 Philips、Siemens、AMD、OKI等,这些公司以 8051 内核为基础,不断改进、完善推出了各式各样指令兼容产品,这些产品统一称为 8051 单片机。

在嵌入式处理器中,单片机在使用量上是最多的,其中市场占有率又以 8051 兼容产品为最大,已经达到数百个品种。不同的产品功能可能有很大的不同,但都是由 MCS-51 内核为基础发展而来,这里以 Intel 8051 为例分析这类单片机原理。

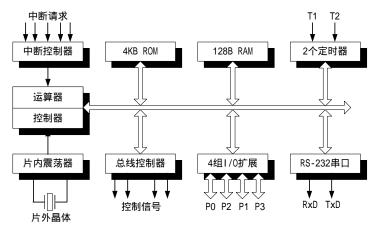

#### 2.4.18051 单片机结构

8051 单片机采用的是哈佛结构,程序空间和数据空间分别寻址。除了一个 8 位处理器核心外,还集成了中断控制器、RAM、ROM、定时器和 UART (Universal Asynchronous Receiver/Transmitter,通用异步收发器),在单个芯片上实现了整套计算机小系统,见图 2.3 所示。

图 2.3 8051 单片机原理结构

#### 8051 单片机有以下主要特征:

- 1) 8 位的微处理器,适合控制领域的应用。

- 2) 集成 128B 的片内 RAM 和 4KB 的片内 ROM,在一些小型应用中,不需要扩展外部存储器,使系统更加简洁,降低了系统成本,同时提高了系统的可靠性。

- 3) 四个 8 位并行 I / O 接口 P0~P3, 提供共计 32 个双向且可独立寻址的 I/O 信号。

- 支持片外存储器扩展,能够寻址 64KB 外部程序存储器和 64KB 外部数据存储器。

- 5) 两个定时器 / 计数器,每个定时器 / 计数器都可以设置成计数方式,用以对外部事件进行计数,也可以设置成定时方式。

- 6) 五个中断源的中断控制系统。

- 7) 一个全双工 UART 的串行通信接口,用于实现系统与其它计算机之间的串行通信。

- 8) 集成片内振荡器和时钟产生电路,但石英晶体和微调电容需要外接,为单片机提供最大 12MHz 的工作时钟。

- 9) 支持 4us 执行周期的乘法指令和除法指令。

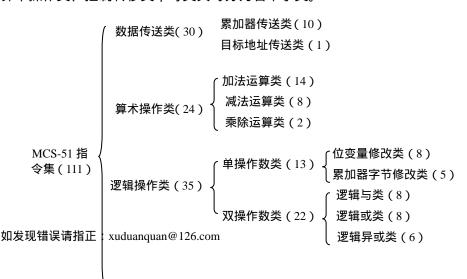

#### 2.4.2 MCS-51 指令系统

MCS-51 指令系统包括 111 条指令,按功能分为 4 大类:数据传送类、逻辑操作类、算术操作类、控制转移类,每类又可分为若干子类。

# 控制转移类(22) { 无条件调用、返回转移类(7) 条件转移类(13) 其它类(2)

#### 图 2.4 MCS-51 指令分类

#### 1) 数据传送类指令

8051 单片机中存放操作数的空间有片内存储器和片外存储器 ,片内存储器又包括工作寄存器、堆栈等数据存储器和累加器等特殊功能寄存器。数据传送指令把立即数或这些空间中的数据传到另一个空间。数据传送指令也可以分为数据传送和数据交换两类。

2) 算术运算类指令

这类指令包括加、减、乘、除四种指令。

3) 逻辑操作类指令

逻辑操作指令包括单操作数指令和双操作数指令两类。单操作数指令中的操作数是累加器或任何可直接寻址位。双操作数指令包含逻辑与、逻辑或、逻辑异或指令三种。

4) 控制转移类指令

MCS-51 指令集有 22 条转移指令,其中除了无条件调用返回转移指令和条件转移指令外,还有 1 条中断返回指令和 1 条空操作指令。

#### 2.5ARM 处理器原理

#### 2.5.1 ARM 技术的发展

说到 ARM,有两方面的含义,一方面指是 ARM 公司,另一方面指基于 ARM IP (Intellectual Property,知识产权)核的嵌入式微处理器。

1990 年 11 月 ARM 成立于英国,原名 Advanced RISC Machine 有限公司,是苹果电脑、Acorn 电脑集团和 VLSI Technology 的合资企业。1991 年 ARM 推出首个嵌入式 RISC 核心——ARM6 系列处理器后不久, VLSI 率先获得授权,一年后夏普和 GEC Plessey 也成为授权用户,1993 年德州仪器和 Cirrus Logic 亦签署了授权协议,从此 ARM 的知识产权产品和授权用户都急剧扩大。

ARM 是一家微处理器技术知识产权供应商,它即不生产芯片、也不销售芯片,只设计 RISC 微处理器,这些微处理器的知识产权就是公司的主要产品。

ARM 知识产权授权用户众多 ,全球 20 家最大的半导体厂家中有 19 家是 ARM 的用户 ,全世界有 70 多家公司生产 ARM 处理器产品。ARM 微处理器应用范围广泛 ,包括汽车电子、消费电子、多媒体产品、工业控制、网络设备、信息安全、无线通信等等。目前 ,基于 ARM 技术的微处理器占据 32 位 RISC 芯片 75%的市场份额。

#### 2.5.2 ARM 体系结构

#### 2.5.2.1 ARM 指令系统的版本

ARM 指令系统共定义了 6 个版本。从版本 1 到版本 6 , 指令集功能越来越丰富 , 另外 在发展过程中还提出了几套扩展指令集。下面首先介绍 6 个版本的指令系统。

1) 版本 1

这个版本只支持26位地址空间,没有在商业产品中使用,包括以下指令:

- 处理乘法指令外的基本数据处理指令。

- 处理字节、字和多字的读取和写入指令。

- 包括子程序调用指令在内的跳转指令。

- 供操作系统使用的软件中断指令。

- 2) 版本 2

该版本也只支持 26 位地址空间,现在已经不再使用。与版本 1 相比,版本 2 增加了下列指令:

- 乘法指令和乘加法指令。

- 支持协处理器的指令。

- 对于快速中断模式,提供额外的两个备份寄存器。

- SWP 指令和 SWPB 指令

- 3) 版本3

该版本与以前的版本发生较大变化,改进如下:

- 地址空间扩展到 32 位,除了版本 3G(版本 3的一个变种)外的其他版本向前兼容,支持 26 位地址空间。

- 当前程序状态信息从原来的 R15 寄存器移到一个名为 CPSR (Current Program Status Register, 当前程序状态寄存器)的新寄存器中。

- 增加 SPSR (Saved Program Status Register, 备份的程序状态寄存器), 用于在程序被异常中断时,保存被中断程序的状态。

- 增加了两种处理器模式,使操作系统代码可以方便地使用数据访问中止异常、指令预取中止异常和未定义指令异常。

- 增加了指令 MRS 和指令 MSR,用于访问 CPSR 寄存器和 SPSR 寄存器。

- 修改了原来从异常中返回的指令。

- 4) 版本 4

该版本明确定义了哪些指令会引起未定义指令异常,另外不再要求与以前的 26 位地址空间兼容。与版本 3 相比,版本 4 增加了以下指令:

- 半字的读取与写入指令

- 读取带符号的字节和半字数据的指令

- 增加了 T 变种,可以使处理器状态切换到 Thumb 状态,在该状态下指令集是 16 位的 Thumb 指令集。

- 增加了处理器的特权模式。

- 5) 版本 5

与版本4比,版本5增加或修改了以下指令:

- 提高了 T 变种中 ARM/Thumb 混合使用的效率。

- 对于 T 变种的指令和非 T 变种的指令使用相同的代码的生成技术。

- 增加了前导零计数指令,可以使整数除法和中断优先级排队操作更为有效。

- 増加了软件断点指令。

- 为协处理器器设计提供了更多的可选择的指令。

- 更加严格地定义了乘法指令对条件标志位的影响。

- 6) 版本 6

版本 6 的主要特点是增加了 SIMD (Single Instruction Multiple Data,单指令多数据) 指令。SIMD 指令可以使音频/视频处理性能提高 4 倍。ARM 指令系统版本 6 首先在 2002

年发布的 ARM11 处理器中使用。

#### 2.5.2.2 ARM 指令系统的扩展指令集

除了几个版本的基本指令集外,ARM 体系结构中还定义几种扩展指令集,分别介绍如下。

# 1) Thumb 指令集 ( T 变种 )

Thumb 是将 ARM 指令集的一个子集重新编码而形成的一个指令集。一般 ARM 指令长度为 32 位,而 Thumb 指令长度为 16 位。使用 Thumb 指令集可以得到密度更高的代码,有利于控制产品成本。但因为 Thumb 是精简版本,因此完成同样的功能需要更多的指令,在对任务执行速度要求苛刻的场合使用 ARM 指令集更合适。

目前 Thumb 有两个版本,版本 1 适用 ARM 指令系统版本 4,而版本 2 试用 ARM 指令系统版本 5。

# 2) 长乘法指令(M变种)

M 变种增加了两条用语长乘法操作的 ARM 指令,一条用于实现 32 位整数乘以 32 位整数,生成 64 位整数的长乘法操作;另一条指令用于实现 32 位整数乘以 32 位整数,然后再加上 32 位整数,生成 64 位整数的长乘加操作。

3) 增强型 DSP 指令 (E 变种)

E 变种包含一些附加指令,这些指令用于增强处理器对一些典型 DSP 算法的处理性能。 主要包括:

- ▶ 几条新的实现 16 位数据乘法和乘加操作的指令。

- > 实现饱和的带符号数的加减操作的指令。

- 进行双字数据操作的指令。

- cache 预取指令 PLD。

- 4) Java 加速器 Jazelle (J 变种)

Jazelle 技术使得在单个处理器上可以同时运行 JAVA 应用程序、操作系统和其他应用程序。与 Java 虚拟机相比,Jazelle 使 Java 代码运行速度提高了 8 倍,而功耗降低 80%。

5) ARM 多媒体功能扩展(SIMD 变种)

SIMD (Single Instruction Multiple Data,单指令多数据)扩展使 ARM 处理器的音/视频处理性能提高4倍,同时保持系统的低功耗。其主要特点如下:

- 可以同时进行两个 6 位操作数或者 4 个 8 位操作数的运算。

- 提供小数算术运算。

- ▶ 用户可一定饱和运算的模式。

- 两套 16 位操作数的乘加/乘减运算。

- > 32 位乘以 32 位的小数 MAC。

- ▶ 同时 8 位/16 位选择操作。

#### 2.5.2.3 ARM/Thumb 体系结构版本的类型

ARM 指令集有 6 个版本,另有 T 变种、M 变种、E 变种、J 变种、SIMD 变种等多个扩展,实际在处理器的应用中有多种组合,以下是各主要版本的命名方式:

| 名称     | ARM 指令<br>集版本 | T 变种及其<br>版本 | M 变种 | E <b>变种</b> | J 变种 | SIMD 变种 |

|--------|---------------|--------------|------|-------------|------|---------|

| ARMv3  | 3             | 无            | 否    | 否           | 否    | 否       |

| ARMv3M | 3             | 无            | 是    | 否           | 否    | 否       |

| ARMv4xM   | 4 | 无    | 否 | 否    | 否 | 否 |

|-----------|---|------|---|------|---|---|

| ARMv4     | 4 | 无    | 是 | 否    | 否 | 否 |

| ARMv4TxM  | 4 | 版本1  | 否 | 否    | 否 | 否 |

| ARMv4T    | 4 | 版本1  | 是 | 否    | 否 | 否 |

| ARMv5xM   | 5 | 无    | 否 | 否    | 否 | 否 |

| ARMv5     | 5 | 无    | 是 | 否    | 否 | 否 |

| ARMv5TxM  | 5 | 版本 2 | 否 | 否    | 否 | 否 |

| ARMv5T    | 5 | 版本 2 | 是 | 否    | 否 | 否 |

| ARMv5TexP | 5 | 版本 2 | 是 | 部分指令 | 否 | 否 |

| ARMv5TE   | 5 | 版本 2 | 是 | 是    | 否 | 否 |

| ARMv5TEJ  | 5 | 版本 2 | 是 | 是    | 是 | 否 |

| ARMv6     | 6 | 版本 2 | 是 | 是    | 是 | 是 |

表 2.1 ARM/Thumb 版本命名及意义 ( **來自参考文献 2 有待确认、补充!!**)

# 2.5.3 ARM 处理器核 ( **來自参考文献 2 有待确认、补充!! 表是ARM 简介 PPT 里的** )

ARM 处理器核有 6 个系列:ARM7、ARM9、ARM9E、ARM10E、SecurCore 以及最新的 ARM11 系列 , 另外 Intel 也推出两个 ARM 处理器系列——XScale 和 StrongARM。

ARM7 采用 ARMV4T 体系结构,分为三级流水,空间统一的指令与数据 Cache,平均功耗为 0.6mW/MHz,时钟速度为 66MHz,每条指令平均执行 1.9 个时钟周期。

ARM7 系列微处理器的主要应用领域为:工业控制、Internet 设备、网络和调制解调器设备、移动电话等多种多媒体和嵌入式应用。ARM7 系列微处理器包括如下几种类型的核:ARM7TDMI、ARM7TDMI-S、ARM720T、ARM7EJ。其中,ARM7TMDI 是目前使用最广泛的 32 位嵌入式 RISC 处理器,属低端 ARM 处理器核。

|            | ARM7 性能特征               |                     |           |              |       |     |         |  |  |  |  |

|------------|-------------------------|---------------------|-----------|--------------|-------|-----|---------|--|--|--|--|

|            | Cache 大<br>小(指令/<br>数据) | 紧耦合存<br>储器<br>(TCM) | 存储管理<br>器 | AHB 总线<br>接口 | Thumb | DSP | Jazelle |  |  |  |  |

| ARM7TDMI   | 无                       | 无                   | 无         | 有            | 有     | 无   | 无       |  |  |  |  |

| ARM7TDMI-S | 无                       | 无                   | 无         | 有            | 有     | 无   | 无       |  |  |  |  |

| ARM7EJ-S   | 无                       | 无                   | 无         | 有            | 有     | 有   | 有       |  |  |  |  |

| ARM720T    | 8k                      | 无                   | MMU       | 有            | 有     | 无   | 无       |  |  |  |  |

表 2.2 ARM7 性能特征

ARM9 采用 ARMV4T 结构,五级流水处理以及分离的指令 Cache 和数据 Cache,平均功耗为 0.7mW/MHz。时钟速度为 120MHz-200MHz,每条指令平均执行 1.5 个时钟周期。 ARM9 系列包括 ARM920T、ARM922T 和 ARM940T3 种类型,主要应用在掌上电脑、多媒体终端、通讯终端、网络设备、汽车电子等领域。

|         | ARM9 性能特征 |       |      |        |       |     |         |  |  |  |  |

|---------|-----------|-------|------|--------|-------|-----|---------|--|--|--|--|

|         | Cache 大   | 紧耦合存  | 存储管理 | AHB 总线 | Thumb | DSP | Jazelle |  |  |  |  |

|         | 小(指令/数    | 储器    | 器    | 接口     |       |     |         |  |  |  |  |

|         | 据)        | (TCM) |      |        |       |     |         |  |  |  |  |

| ARM920T | 16K/16K   | 无     | MMU  | 有      | 有     | 无   | 无       |  |  |  |  |

| ARM922T | 8K/8K     | 无     | MMU  | 有      | 有     | 无   | 无       |  |  |  |  |

| ARM940T | 4K/4K     | 无     | MMU  | 有      | 有     | 无   | 无       |  |  |  |  |

#### 表 2.3 ARM9 性能特征

ARM9E 采用 ARMv5 体系结构,使用单一的处理器内核提供了微控制器、DSP、Java 应用系统的解决方案,极大的减少了芯片的面积和系统的复杂程度。ARM9E 系列微处理器提供了增强的 DSP 处理能力,很适合于那些需要同时使用 DSP 和微控制器的应用场合。

| ARM9E 性能特征 |               |       |      |       |       |     |         |  |  |

|------------|---------------|-------|------|-------|-------|-----|---------|--|--|

|            | Cache 大小(指    | 紧耦合存  | 存储管理 | AHB 总 | Thumb | DSP | Jazelle |  |  |

|            | 令/数据)         | 储器    | 器    | 线接口   |       |     |         |  |  |

|            |               | (TCM) |      |       |       |     |         |  |  |

| ARM926EJ-S | 4-128K/4-128K | 有     | MMU  | 双 AHB | 有     | 有   | 有       |  |  |

| ARM946EJ-S | 4-1MB/4-1MB   | 有     | MMU  | AHB   | 有     | 有   | 无       |  |  |

| ARM966EJ-S | 无             | 有     | 无    | AHB   | 有     | 有   | 无       |  |  |

表 2.4 ARM9E 性能特征

ARM10E 系列微处理器具有高性能、低功耗的特点,采用了 ARMv5 体系结构。与同等的 ARM9 器件相比较,在同样的时钟频率下,性能提高了近 50%,同时,ARM10E 系列微处理器采用了两种先进的节能方式,使其功耗极低。

|             | ARM10E 性能特征         |            |           |              |       |     |         |  |  |  |

|-------------|---------------------|------------|-----------|--------------|-------|-----|---------|--|--|--|

|             | Cache 大小(指<br>令/数据) | 紧耦合存<br>储器 | 存储管理<br>器 | AHB 总<br>线接口 | Thumb | DSP | Jazelle |  |  |  |

|             |                     | (TCM)      |           |              |       |     |         |  |  |  |

| ARM1020E    | 32K/32K             | 无          | MMU       | 双 AHB        | 有     | 有   | 无       |  |  |  |

| ARM1022E    | 16K/16K             | 无          | MMU       | 双 AHB        | 有     | 有   | 无       |  |  |  |

| ARM1026EJ-S | 可变                  | 有          | MMU       | 双 AHB        | 有     | 有   | 有       |  |  |  |

表 2.5 ARM10E 性能特征

ARM11 系列处理器采用 ARMv6 体系,ARM11 处理器工作频率为  $350M\sim500MHz$ ,并可上升到 1GHz,能提供更高的性能。另外,通过动态调整时钟频率和工作电压,实现性能和功耗间的平衡,以满足应用的不同需要。在采用 0.13um 工艺,1.2V 工作电压时,ARM11 处理器的功耗可以低至 0.4mW/MHz。

|             | ARM11 性能特征          |                     |           |                |     |         |      |          |  |  |

|-------------|---------------------|---------------------|-----------|----------------|-----|---------|------|----------|--|--|

|             | Cache 大小(指<br>令/数据) | 紧耦合存<br>储器<br>(TCM) | 存储管理<br>器 | AHB 总<br>线接口   | DSP | Jazelle | SIMD | 浮点<br>运算 |  |  |

| ARM1136J-S  | 4-64K               | 有                   | MMU       | 四个 64<br>位 AHB | 有   | 无       | 有    | 无        |  |  |

| ARM1136JF-S | 4-64K               | 有                   | MMU       | 四个 64<br>位 AHB | 有   | 无       | 有    | 有        |  |  |

表 2.6 ARM11 性能特征

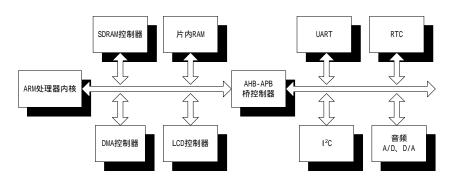

#### 2.5.4 ARM 处理器的片内总线

ARM 公司设计各种处理器内核,并将设计授权给其他半导体厂家,这些厂家在 ARM IP 核的基础上,集成各种外部控制,生产出自己的 ARM 兼容 SOC 处理器产品。在 SOC

的设计中,除了处理器内核外,还有大量控制功能模块,模块之间的连接一般采用片内总 线实现。

片内总线有多种规范,如 IBM CoreConnect 总线、OCP 总线、Wishbone 总线、Avalon 总线等。为了规范 ARM 兼容 SOC 设计,ARM 公司制定了 AMBA 片内总线标准,目前市场上的 ARM 处理器大多按照 AMBA 结构设计。

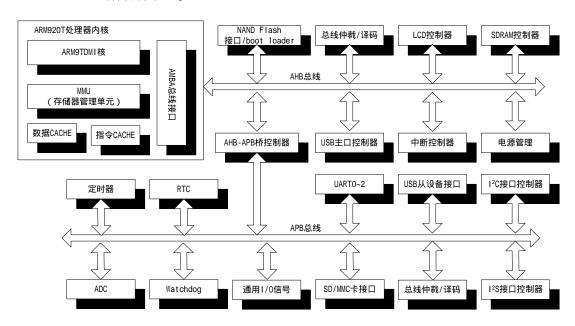

实际产品中 AMBA 2.0 标准应用较普遍,该标准包括四个部分:AHB(Advanced High-Performance Bus)、ASB(Advanced System Bus)、APB(Advanced Peripheral Bus)和 Test Methodology。在 ARM SOC 设计中,常见 AHB 和 APB 二级总线的结构设计,AHB 负责 ARM 处理器内核与 DMA 控制器、片内存储器、SDRAM 控制器、LCD 控制器、快速以太网控制器等高速模块的连接,而 APB 总线则用于连接一些慢速的设备,如 UART 控制器、RTC、I<sup>2</sup>C 控制器等。两条总线通过 AHB-APB 桥控制器互连,一起组成 SOC 芯片的片内架构,如图 2.5 所示。

图 2.5 采用 AMBA 片内总线标准的 SOC 典型结构

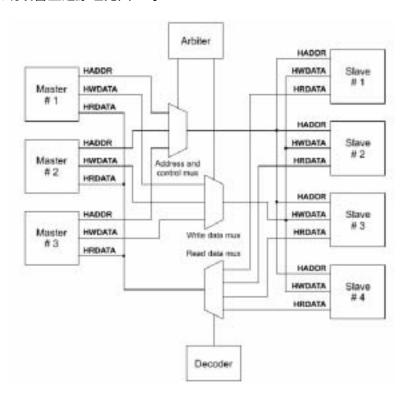

AHB 系统由 Master (主设备)、Slave (从设备)、Infrastructure (总线逻辑)三部分组成。所有的 AHB 总线操作都由 Master 发出,而由 Slave 响应 Master 发起的操作。AHB 系统中可同时存在多个主设备,存在总线竞争,因此需要总线仲裁(Arbiter)。

AHB 从设备都映射到不同的地址空间,主设备发起操作时给出对应的地址,由集中的地址译码器(Decoder)为地址范围内的 Slave 产生选择型号。

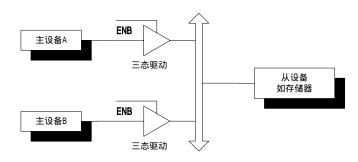

在计算机总线中,设备对总线的驱动常采用三态驱动器,当设备不应该向总线发出信号时,驱动器输出为高阻态,即将设备与总线断开,避免影响总线的工作。其原理如图 2.6 所示,当驱动使能信号"ENB"无效时,驱动器关闭,对应的设备与总线隔离,实际应用中,一般控制、地址信号是单向驱动,而数据信号是双向驱动。

图 2.6 三态总线原理

AHB 总线没有采用传统的三态驱动方式,而采用复用器为通讯的主、从设备建立连接,复用器起着多路开关的作用,当根据总线仲裁的结果选通获得总线控制的主设备,或根据地址译码的结果选择对应的从设备。

AHB 系统设备互连原理见图 2.7。

图 2.7 AHB 系统中设备互连示意图

图中,三个主设备都可以对从设备发起总线操作,由仲裁器判定获得总线控制的设备。 三个主设备的地址和控制信号由一个复用器集中控制,获得总线控制权的主设备的信号可以穿过复用器送到从设备。

在 AHB 系统中,设备采用彼此独立的读、写数据总线,主设备的写数据总线通过仲 裁器控制的复用器送到从设备,从设备的读数据总线通过地址译码控制的复用器送到主设 备。

APB 总线用于连接 UART、 $I^2$ C、RTC 类的慢速设备,结构比 AHB 简单。APB 不是 多主(Multi-Master)总线,在 APB 系统里,唯一的主设备就是 AHB-APB 桥控制器,因此不需要总线仲裁管理。

# 2.5.5 S3C2410 处理器

S3C2410 是一个 32 位 ARM9 处理器,采用 ARM920T 内核,具有高性能、低功耗、低价格的特点,适合应用在各种低成本、低功耗的嵌入式系统中。

为了简化硬件设计、控制系统综合成本、降低系统功耗,除了 ARM9 处理器内核外, S3C2410 处理器基于 AMBA 片内总线结构集成了大量的功能模块,最大限度地减少扩展

#### 外部控制器的需要。在处理器集成的功能如下:

- ARM920T 处理器核

- SDRAM 控制器及片选信号发生逻辑

- 集成 LCD 控制器,支持彩色 STN 或 TFT 显示器

- 多通道 DMA 控制器

- 3 通道 UART

- 集成 I<sup>2</sup>C 控制器和 I<sup>2</sup>S 控制器

- 集成 SD 接口控制器

- USB 主/从控制器

- 多诵道定时器

- 看门狗定时器

- 多通道 ADC 及触摸屏接口

- RTC (Real Time Controller, 实时时钟控制器)

- 片上 PLL 时钟发生器

S3C2410 结构见图 2.8。

图 2.8 S3C2410 原理结构

如图所示,S3C2410 是一个基于 ARM920T 处理器内核 SOC 处理器,采用了 ARM AMBA 总线结构,包括 AHB 片内高速系统总线和 APB 片内低速设备总线。AHB 总线上的功能模块包括 SDRAM 控制器、LCD 控制器、USB 主设备控制器等,APB 总线上的功能模块包括 UART 串口控制器、USB 从设备控制器、 $I^2C$  总线控制器、 $I^2S$  总线控制器、RTC、Watchdog、ADC 等。

ARM920T 是一种 ARM9TDMI 通用微处理器,由 ARM9TDMI 核、cache 及 MMU 组成,支持 32 位 ARM 指令集和 16 位 Thumb 指令集。ARM920T 采用 Harvard 结构,指令、数据 cache 分离,各为 16KB。

S3C2410 集成了 NAND Flash 接口,可以无缝地连接 NAND Flash 芯片,而且内部固化 NAND Flash 的 boot loader 程序,可以在系统复位后从 NAND Flash 中引导启动代码。 当然 S3C2410 也可以象其它普通计算机系统一样,在复位后直接从 NOR Flash 中执行启动代码。

# 2.6 嵌入式 x86 处理器

# 2.6.1 嵌入式 x86 处理器发展

x86 处理器是指兼容 x86 指令集的处理器,目前主要的生产厂家包括 Intel、AMD、VIA 等。目前绝大多数的个人计算机,包括台式机和便携机都采用 x86 处理器。

x86 处理器最早由 Intel 公司推出,在 PC 还未出现之前,早期的 x86 处理器是为嵌入式应用设计,如 4004、8008、8080 等。1981 年,美国 IBM 公司将 Intel 的 8088 处理器应用于其研制的 PC 中,进而开创了广阔的个人计算机市场。由于 PC 市场的巨大需求,x86 处理器技术发展上由最初的嵌入式应用转向信息处理应用,PC 成为x86 处理器的主战场,虽然嵌入式应用中仍能看到 x86 的身影,但已经变为从属地位。

随着计算机技术和网络技术的发展,由计算机技术(Computer)、通信技术(Communication)及消费类电子(Consumer Electronics)相融合而形成的 3C 产品成为新的发展方向,3C 产品的兴起标志着计算机发展进入后 PC 的时代。在后 PC 时代,手机、电视、机顶盒、掌上电脑、影碟机等 3C 设备部分地取代 PC 机,实现信息处理、多媒体播放、网络通讯等功能。嵌入式系统是后 PC 时代的技术基础。

因为 PC 的兴起, x86 处理器从最初的嵌入式控制应用走向通用计算应用。而随着以 3C 产品为代表的后 PC 时代的来临, x86 处理器在嵌入式系统中应用需求的越来越大, 主要的 x86 处理器厂家对该领域都投入了很大的力量,并推出了各自的系列产品,如 AMD的 Geode GX/LX/NX 系列、Intel 的 Atom 处理器系列、VIA 的等 Eden 处理器系列等。

x86 计算机技术经过长期的发展,积累了极其丰富的硬件、软件资源。嵌入式 x86 处理器都保持了对传统技术良好的兼容性,因此能充分利用现在的技术资源,性价比高、技术成熟、开发难度低、开发周期短。

#### 2.6.2 Geode x86 处理器

AMD 有多种嵌入式 x86 处理器,其中 Geode 系列是典型的嵌入式 x86 处理器。Geode 有几个子系列,若干种型号,见表 1.7。

| 处理器系列    | 处理器型号   | 时钟频率    | 内核电压  | 典型功耗 | 最大功耗       |

|----------|---------|---------|-------|------|------------|

|          | NX 1250 | 667MHz  | 1.1V  | 6W   | 9W         |

| Geode NX | NX 1500 | 1.0GHz  | 1.0V  | 6W   | 9 <b>W</b> |

|          | NX 1750 | 1.25GHz | 1.25V | 14W  | 25W        |

|          | LX 700  | 433MHz  | 1.2V  | 0.8W | 3.1W       |

| Geode LX | LX 800  | 500MHz  | 1.25V | 0.9W | 3.6W       |

|          | LX 900  | 600MHz  | 1.4V  | 1.5W | 5.1W       |

|          | GX 466  | 333MHz  | 1.5V  | 0.9W | 3.5W       |

| Geode GX | GX 500  | 366MHz  | 1.5V  | 1.0W | 3.5W       |

|          | GX 533  | 400MHz  | 1.5V  | 1.1W | 3.5W       |

#### 表 1.7 Geode 系列嵌入式处理器

# 2.6.3 Geode GX 处理器原理

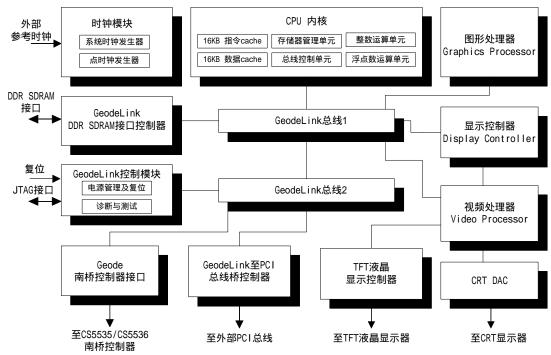

这里以 Geode GX 为例分析 Geode 处理器的原理。GX 处理器有三个型号:GX533、GX500、GX466,核心工作频率分别是 400MHz、366MHz、333MHz,具有低功耗的优点,运行中的典型功耗分别是 1.1W、1.0W、0.9W,工作中不需要散热风扇,适合瘦客户机、掌上电脑、机顶盒、小型终端设备及工业控制等嵌入式应用领域。GX 处理器具有低功耗、多功能、低价格、广泛的兼容性等特点,应用中总是与 CS5535 或 CS5536 南桥配合使用。GX 处理器主要特性有:

- 1.5V 核心电压,1.1W 的典型功耗,不需要散热风扇

- 32 位 x86 处理器,支持 MMX 和 3Dnow!扩展指令,支持高性能多媒体和二维、 三维图形图像处理

- 32KB 的一级 cache,包括 16KB 指令 cache 和 16KB 数据 cache

- 基于高性能 GeodeLink 片内总线实现处理器内部各功能单元间的联接

- 集成图形控制器,支持TFT和CRT两种显示接口,CRT接口内置视频DAC,分辨率可以达到1600x1200x85Hz。该VGA控制器与处理器内核共享系统内存,在BIOS(如General Software的Embedded BIOS)中可对内存占用量进行设置。

- 通过 GeodeLink 至 PCI 的桥控制器扩展外部 PCI 总线,支持 PCI 2.2 总线规范,除了各种普通可扩展 PCI 设备外 GX 的南桥控制器也是该总线上的一个特殊 PCI 设备

- 集成 64 位 DDR SDRAM 存储控制器

- 可编程的时钟发生器,可通过软件设置倍频数调整核心时钟频率和图形加速器工作频率

GX 处理器功能丰富,与 CS5535/5536 南桥组合在一起,再扩充外部 DDR 存储器,就构成一个精练的、低成本的 PC 兼容小系统。正因为如此,GX 处理器才被应用到一些低价个人电脑中,如在尼葛洛庞帝(Negroponte)提出的 100 美金电脑里就曾经采用 GX 处理器。

图 2.9 给出了 Geode GX 处理器的原理结构 ,如图所示 ,GX 处理器中除了 x86 内核外 ,还集成传统 PC 主板中的北桥及某些外部控制器的功能 ,如 DDR SDRAM 控制器、PCI 控制器以及 CRT/TFT 液晶显示控制器等。芯片集成度大 ,同时还保持较低的功耗 ,适合嵌入式系统的需要。

图 2.9 Geode GX 处理器原理结构

#### 2.6.3.1 GeodeLink 总线

从图 2.7 中可以看出, GeodeLink 片内总线是 GX 处理器内部各单元互联的核心。

GeodeLink 是 AMD 定义的一个用于 SOC 芯片的系统架构,其片上交换矩阵是一个带宽极高的接口单元,支持最大 6GB/S 的数据传输速率。因为片内图形加速器与 CPU 共享系统内存,所以 GeodeLink 的高传输速率是高性能 VGA 接口的保证。

GeodeLink 应用在 GX 处理器和及其南桥控制器 CS5535/CS5536 中,是有效组织众多片上功能单元的核心技术。在 GX 处理器和南桥控制器内,都集成 GeodeLink 片内总线上的接口控制器,实现两个芯片之间的无缝连接。

基于 GeodeLink 的系统结构不影响 Geode 对各种操作系统的支持。Geode 支持的嵌入式操作系统包括 Windows CE、Linux、WinXPe、VxWorks、QNX 等。实际上,只要有适合的设备驱动程序, GeodeLink 架构处理器可以运行任何 x86 兼容的操作系统,包括 DOS、各种桌面 Windows 等。

#### 2.6.3.2 Geode GX CPU 内核

Geode GX 的 x86 内核包括整数单元、x87 兼容的浮点单元、存储器管理单元(MMU) Cache 以及总线控制单元几个组成部分。

GX CPU 内核整数单元支持 8 级流水线 通过其它必要的支持硬件使流水线高效运行。

- 指令预取:从指令 cache 中取出原始指令。

- 指令预解码:提取原始指令数据的前缀字节,该解码操作可以预测下一条指令, 这种预测在流水线出现停顿时可以被限制。

- 指令解码:对指令数据进行完全解码,向指令预取单元提示指令长度,这样预取单元才知道多少个字节以后才是下一条指令的起始位置。

- 指令排队:译码后的 x86 指令排列在 FIFO 中。在该阶段完成有关操作数地址计算的寄存器读操作。

- 地址计算#1:计算操作数的线性地址(如果需要的话),并向数据 cache 发出请求。

- 地址计算#2:返回操作数(如果有的话),并将操作数送到执行单元。

- 执行指令:算术逻辑单元(ALU)对寄存器或数据存储器中的数进行算术或逻辑 运算。

- 回写操作:将指令执行的结果写入寄存器或数据存储器中。

存储器管理单元(MMU)将整数单元提供的线性地址转换成 cache 和总线控制单元使用的实际物理地址。

总线控制单元提供 Geode GX 内核与 GeodeLink 总线的接口,在需要进行外部存储器访问的时候,相应物理地址被送到总线控制单元,总线控制单元则把该操作转换成一个 GeodeLink 总线的访问。

# 2.6.4 CS5535 原理

CS5535 是 Geode GX 处理器的配套芯片, GX 处理器中集成了 CPU 内核及北桥,而 CS5535 则集成了 PC 机主板中的南桥及超级 I/O 的功能。

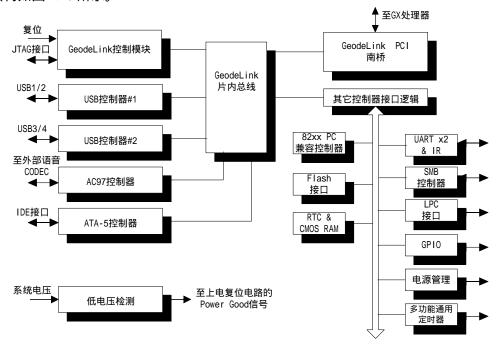

CS5535 集成了很多 I/O 接口,如 IDE 接口、AC97 声卡、USB 接口、实时时钟(RTC) LPC 接口(用于 BIOS 存储器) UART 接口等,还支持电源管理功能。和 GX 处理器一样, CS5535 内部多个功能单元以 GeodeLink 片内总线为中心组成一个整体,并基于 GeodeLink 桥与 GX 处理器实现无缝连接,为系统扩充各种接口及电源管理等功能。CS5535 内部原理结构如图 2.10 所示。

图 2.10 CS5535 原理结构

CS5535 内核及 I/O 部分分别供电 ,I/O 电压为 3.3V ,内核部分工作电压为 1.2V 或 1.5V ,

典型的运行功耗仅为 150mW。该芯片集成了丰富的功能,分别介绍如下:

- GeodeLink PCI 南桥:支持 PCI V2.2 总线规范,实现与 GX 处理器的无缝连接

- GeodeLink 控制模块:实现复位、电源管理及调试/测试接口

- ATA-5 控制器:支持 66MB/S 的 IDE 接口

- Flash 接口:与 IDE 接口的部分信号复用,支持各种标准的 NAND Flash 或 NOR Flash 芯片

- USB 控制器:两个 USB 控制器共提供4个 USB v1.1 接口

- AC97 音频控制器:支持 AC97 v2.1 规范,实现外部音频 codec 的无缝连接

- 传统 PC 的 82xx 控制器:集成两片 8259A 兼容可编程中断控制器;一片 8254 兼容可编程定时/计数器;一片 8237A 兼容 DMA 控制器;两片 16550A/16550 兼容 UART (Universal Asynchronous Receiver/Transmitter)

- IR(红外, Infrared)通信接口:软件山与 16550A/16550 控制器兼容,支持多种 红外接口协议

- SMB( System Management Bus )控制器:兼容 Intel System Management Bus、Philips I<sup>2</sup>C 及 ACCESS.bus

- LPC(Low Pin Count)接口:支持 Intel 接口规范 v1.1,多用于外部 BIOS 存储器

- GPIO (General Purpose I/O):通用目的 I/O 接口信号,可编程为各种工作方式

- 多功能通用定时器:实现定时器相关功能

- RTC (Real-Time Clock): 实时时钟,可由外部电池供电,提供年、月、星期、日、时、分、秒等日历与时间信息

- CMOS RAM:由电池供电的 242 字节 RAM 区,存储需要掉电保护的系统参数

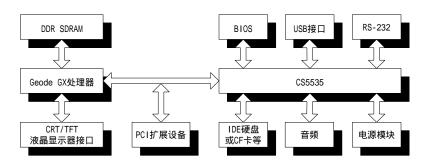

# 2.6.5 基于 Geode GX 处理器的系统结构

GX 处理器集成了 CPU 内核、北桥、显示控制器 ,CS5535/CS5536 集成了南桥及 Super I/O 的各项功能 , 二者通过外部总线无缝连接 , 以这两个芯片组合为基础可以实现结构简单、功能完整的 PC 兼容嵌入式计算机系统 , 该类系统具有结构紧凑、功耗低、无须散热风扇、综合成本低等优点。图 2.11 是基于 GX 处理器和 CS5535 南桥控制器的计算机系统原理结构。

图 2.11 基于 GX 处理器的嵌入式计算机系统原理结构

#### 2.7 DSP 处理器

平时说到 DSP 可能有两种含义,一种是指数字信号处理理论,另一种是指用于实现数字信号处理算法的专用芯片,即数字信号处理器,本书特指后一种含义。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤

波、估值、增强、压缩、识别等处理,以得到符合需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。数字信号处理在理论上的发展推动了数字信号处理应用的发展。反过来,数字信号处理的应用又促进了数字信号处理理论的提高。而数字信号处理的实现则是理论和应用之间的桥梁。

在数字信号处理的应用中,要实现各种数字信号处理算法。这些算法的实现有两种方式,一种是在通用计算机上编程实现;另一种是在专门的数字信号处理芯片上编程实现。 在实时信号处理应用中,因为速度、成本、体积等各种约束,不便或不能使用通用计算机 实现数字信号处理算法,这时需要使用数字信号处理器。

#### 2.7.1 DSP 与普通处理器的区别

DSP 的主要用于实现数字信号处理算法,是一种特殊的处理器。在数字信号处理算法中有一些特殊计算要求,如乘法计算、尤其是"乘-加"计算量很大,一般的处理器实现这些计算的效率较低。为提高计算速度,需要设计一些专用指令,并优化处理器结构,符合这些特殊设计的处理器就是 DSP。

与普通处理器相比具有以下特点:

#### ● 支持密集的乘法运算

数字信号处理算法中往往有大量的乘法计算, DSP 使用专门的硬件来实现单周期乘法,另外还增加了专门的乘法-累加硬件实现高效率的"乘-加"计算。

#### ● 采用哈佛结构

使用冯.诺依曼存储器结构的处理器中,程序指令和数据共用一个存储器空间,不能同时寻址。通常,做一次乘法会发生4次存储器访问,需要四个指令周期。

大多数 DSP 采用了哈佛结构,程序指令和数据分开存储,并且可以通过彼此独立的不同总线同时寻址,这种存储结构使 DSP 得以实现单周期的乘法指令。

# ● 支持零开销循环

所谓零开销循环是指处理器在执行循环时,不用花时间去检查循环计数器的值、条件 转移到循环的顶部、将循环计数器减 1。

DSP 算法有一个共同的特点,即大多数的处理时间是花在执行较小的循环上,因此大多数的 DSP 都有专门的硬件,实现零开销循环。

## ● 采用定点计算

大多数 DSP 使用定点计算,使用浮点的 DSP 比较少,因为定点处理器比浮点处理器 更容易实现高速度、低价格。为了保证计算的准确性,DSP 处理器在指令集和硬件方面都 支持饱和计算、舍入和移位。

#### ● 支持特殊的寻址方式

为了适应实现数字信号处理算法的需要 ,DSP 处理器往往支持一些普通处理器没有的特殊寻址模式 , 如循环寻址、位倒序寻址等。

#### ● 应用具有实时性要求

一般 DSP 的应用都有实时性的要求,也就是说特定的任务要求在特定的时间里被完成。如用 DSP 实现视频编码的应用中,视频采集速率为 25 帧/s,帧间隔为 40ms,平均每帧编码时间必须小于 40ms,否则就会出现丢帧的现象。

在用 DSP 实现数字信号处理算法时,最大的工作量往往是提高软件执行的效率、满足算法实时性要求,主要通过优化程序结构、采用高效的计算指令、提高指令执行的并行度、提高 cache 命中率等措施实现实时处理的目的。

#### ● 开发环境有特殊要求

和普通处理器一样,在 DSP 上开发应用软件也需要使用集成开发环境,但 DSP 的开 发环境有特殊的要求。

DSP 是一种嵌入式处理器,采用交叉开发的模式,开发计算机采用通用计算机,一般是 PC 机,而运行目标是 DSP 硬件系统。DSP 开发环境一般提供软件仿真工具,在开发机上为 DSP 软件提供模拟的测试运行环境。

另外 DSP 应用有实时性的要求,需要对代码进行高度优化,所以 DSP 的开发环境提供一些专门工具,以支持软件优化工作。

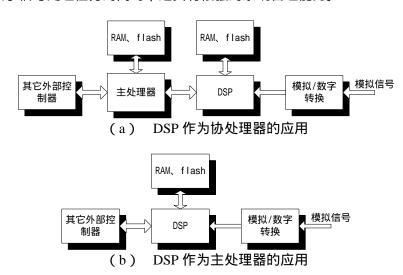

#### 2.7.2 DSP 的应用形式

DSP 是一种嵌入式处理器,实际应用中有两种形式,一种是作为主处理器的协处理器,专门负责完成数字信号处理的有关计算操作,并与主处理器交换计算结果;在另一种应用形式中,DSP 不仅完成数字信号处理的任务,还独立完成整个嵌入式系统的管理,这时系统中由 DSP 担当起系统的主处理器角色。

在普通嵌入式处理器里集成 DSP 处理核,或增强 DSP 的功能,使之具备通用处理器的功能,这是嵌入式处理器一种技术融合的发展趋势。例如 TI (Texas Instrument)设计的双核处理器 OMAP 和 DaVinci,在单个芯片内集成了 ARM 核和 DSP 核,从而使处理器在高效执行数字信号处理任务的同时,还具有很强的系统管理能力。

图 2.12 DSP 在嵌入式系统中的两种应用形式

#### 2.7.3 TMS320DM642 处理器

TI 公司是世界上最大的 DSP 芯片供应商,其 DSP 市场份额占全世界份额近 50%。其 DSP 产品主要分为三大系列,即 TMS320C2000 系列、TMS320C5000 系列和 TMS320C6000 系列。

TMS320C6000 系列 DSP 具有高性能,最高主频超过 1 GHz,包含定点 C62x 和 C64x 以及浮点 C67x,适合宽带网络数据处理、数字图像处理、数字视频编码、雷达信号处理等应用。

TMS320C5000 系列 DSP 提供性能、外围控制接口、小型封装和电源效率的优化组合,

适合便携式上网、语音处理及对功耗有严格要求的应用。该系列包括代码兼容的定点 C54x 和 C55x。

TMS320C2000 系列 DSP 针对控制领域做了优化配置,集成了众多的外部控制接口,适合逆变器、马达、机器人、数控机床、电力等应用领域。该系列包括 16 位 C24xx 和 32 位 C28xx 的定点 DSP。由于 C2000 定位在控制领域,片内集成了大量接口控制器,如 I/O、SCI、SPI、CAN、A/D 等等,所以 C2000 在完成高速数字信号处理的同时,还能象普通微控制器一样实现系统控制功能,所以 C2000 也常被称为 DSP 控制器。

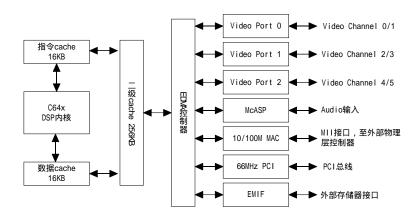

TMS320DM642 是 TI 公司的一款专用于多媒体处理的 DSP ,属于 TMS320C6000 系列中的一个型号,主要用于数字视频、数字音频的编码应用。

DM642 是高性能定点 DSP , 采用 C64x 内核 , 集成了 8 个执行单元 , 每时钟周期最多可同时执行 8 条指令 , 主频可为 500 MHz、600 MHz 或 720 MHz ,最大运行速度分别达到 4000、4800 和 5760 MIPS ( Million Instructions Per Second )。

DM642 采用两级高速缓存结构,第一级包括相互独立 16KB 的指令 cache 和 16KB 的数据 cache。第二级缓存为 256KB ,是一个统一的程序/数据空间,可以整体作为 SRAM 映射到存储空间,也可以整体作为第二级 Cache,或是二者按比例的一种组合来使用。DM642 具有 64 个独立通道的增强型直接存储器访问(EDMA, Enhanced Direct Memory Access)控制器,负责片内二级缓存与外设以及外设之间的数据高速传输。

DM642 是构建多媒体处理系统的理想平台,为此集成了丰富的外部设备接口:

- 三个可配置的双通道视频端口,可以同时接入6路视频

- 集成 McASP (Multichannel Buffered Audio Serial Port), 支持多路数字语音输入

- 64bit 数据宽度的外部外部存储器接口——EMIF, 支持 SDRAM、SRAM、Flash 等不同类型的存储器

- 10/100M 自适应以太网 MAC (Media Access Controller),支持 MII (Media Independent Interface,介质无关接口),在外部扩展以太网物理层控制器(PHY)就可以实现一个完整的网络接口

- 66MHz 32bit 的 PCI 2.2 标准总线接口

- 支持 HPI32 或 HPI16 接口

DM642 中以太网 MAC、PCI 及 HPI 的信号复用芯片的引脚,通过配置信号设置实际的接口模式。当用 DM642 设计多媒体 PCI 卡时,设置为 PCI 接口模式;在嵌入式系统应用中,如果 DM642 作为主控处理器时,可设置为以太网 MAC 接口模式;如果在嵌入式系统应用中 DM642 是多媒体协处理器,外部另有专门的主控处理器,可设置为 HPI 接口模式,DM642 可通过 HPI 接口与主控制器交换数据。

DM642 结构见图 2.13。

图 2.13 TMS320DM642 处理器原理结构

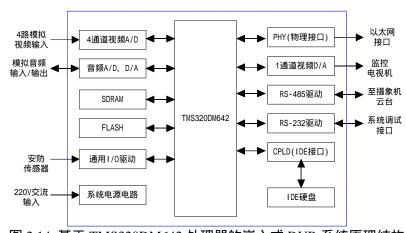

DM642 可以在独立工作的嵌入式系统中作为主控制器使用,在完成多媒体处理任务的同时 实现系统的控制及数据传输功能 图 2.14 给出的是一个基于 DM642 的四通道 DVR (数字硬盘录像机)原理结构。该系统中, DM642 软件目标代码需固化在 Flash 中,系统上电后自动加载运行,在该系统中 DM642 不仅完成音/视频压缩编码,还需要完成系统控制及网络通信功能。

图 2.14 基于 TMS320DM642 处理器的嵌入式 DVR 系统原理结构

图 2.14 DVR 系统中,首先对模拟音/视频数字化,对数字音/视频数据进行压缩编码,并将结果存储在系统硬盘中。通过以太网,管理计算机(一般是 PC 机)可以实时预览 DVR 的各路音/视频或播放其历史录像,这意味着 DM642 处理器要实现对网络接口的驱动及 TCP/IP 协议栈。

通用 I/O 接口用于接入各种安防传感器,如门磁、窗磁、红外传感器、烟雾传感器等。系统支持一路视频回放,摄像机实时视频或历史录像解压缩后的视频可以通过这个通道回放到外接电视机上。RS-485 用于控制云台,调整摄像机的方向,而 RS-232 作为系统的调试端口,外接 RS-232 终端可对系统进行诊断或配置。

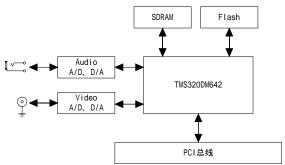

DM642 内置 PCI 控制器,也常以 PCI 卡的形式为计算机扩展多媒体处理功能,如图 2.15。在这种应用中,DM642 的目标代码固化在 Flash 中,但更常用的方法是通过 PCI 卡

设备驱动程序将目标代码下载到 DM642 的 SDRAM 中运行,省去 Flash 芯片,降低了系统的成本。

图 2.15 基干 TMS320DM642 的多媒体处理卡结构

# 2.8 SOC 处理器及实例

# 2.8.1 SOC 处理器类型及优点

根据 SOC 适用的范围,可以把它分为通用 SOC 和专用 SOC。通用 SOC 的适用范围宽,支持一个大类的嵌入式应用,如小型网络终端、带 LCD 显示的仪表等;而专用 SOC 的应用对象非常明确,如调制解调器、路由器、小型 VOIP 网关、可视电话、网络摄像机、手机等。

SOPC (System On Programmable Chip,可编程片上系统)是一种特殊的 SOC,首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC 结合了 SOC 和 PLD、FPGA 各自的优点,一般具备以下基本特征:

- 至少包含一个嵌入式处理器内核

- 具有小容量片内高速 RAM 资源

- ▶ 丰富的 IP Core 资源可供选择

- 足够的片上可编程逻辑资源

- ▶ 处理器调试接口和 FPGA 编程接口

- 可能包含部分可编程模拟电路

- ▶ 单芯片、低功耗、微封装

SoC 将一个嵌入式系统需要的大多数核心功能集成在一个芯片上 基于 SOC 进行嵌入式系统设计有许多优点:

- 1) SOC 将处理器核心及系统常用控制器集成在一个芯片上,使得硬件系统变得非常简洁,极大地减小产品复杂性,并显著降低系统研发成本,缩短产品开发的时间。

- 2) 使用 SOC 处理器可以省去很多外部接口控制芯片,且 SOC 往往在芯片内做了功耗控制的优化设计,因而使用 SOC 处理器可以有效地降低系统功耗。

- 3) 采用 SOC 处理器的嵌入式系统更简洁,因而电路板引线及器件减少,降低 PCB 板设计、制造、焊接的难度。

- 4) 处理器内核与接口控制器在同一个芯片上,可以加快数据传输速度和可靠性。

- 5) 使用 SOC 处理器可以简化 PCB 线路,从而减轻电路板信号传送时所造成的系统信号串扰,改善系统电磁兼容(EMC)特性。

#### 2.8.2 视频编码 SOC 处理器

在视频应用系统中,视频需要实时监视或存储,过去的系统中视频采用模拟信号,通过同轴电缆传输到电视中显示,或通过模拟录像机记录。随着计算机技术和数字信号处理技术的发展,视频应用由模拟系统转到数字系统,视频的传输通过网络,而记录使用大容量硬盘。

数字视频监控系统中关键的一环是视频的压缩编码,因为原始视频数据量太大,不易传输或存储,经过高效编码后,数字视频的数据量可以被压缩一百倍左右。目前常见的视频编码标准包括 MPEG-1、MPEG-2、MPEG-4、H.264 以及中国的视频编码标准——AVS等。

视频编码有软件实现和硬件实现两种方案。现在 PC 性能越来越强,能够轻松实现多路视频的实时编码,因而软编码方案在低成本的应用系统中大量使用。但软编码大量占用计算机资源,在多通道、功能复杂的专业视频应用系统中不易实现较高的稳定性。

在很多专业领域,如视频节目制作、电视广播、安全监控等领域,要求视频质量高、 且系统能长期稳定工作。例如在安全监控领域,一套系统中往往要支持多路视频,而且需 要长期不关机地运行,这些应用中硬编码方案成为首选。

硬件视频编码有 DSP 和 ASIC(专用集成电路)两种。早期数字视频应用中,ASIC 芯片很少或不成熟,价格比较高,DSP 的视频编码应用有很大的发展空间,这方面比较常用的 DSP 包括 Philip 的 Trimedia 和 Ti 的 TMS320DM642 等。DSP 实现视频编码要完成编/解码程序的移植与优化,技术门槛较高。

随着市场的日益扩大,更多的厂家投入到视频编码器的开发中,出现了多种 ASIC 的视频编码解决方案,这些芯片针对性强、集成度高,综合成本相对 DSP 具有一定的优势,尤其在小型多媒体终端产品中更是如此。

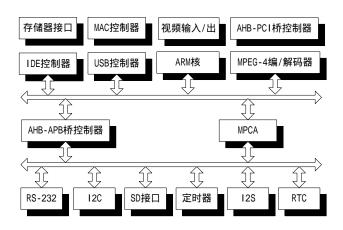

在数字视频应用的嵌入式系统中,除了视频编码器外,还需要有主处理器、视频CODEC(即A/D、D/A)语音CODEC、网络控制器、IDE控制器、RS-232串口控制器、SDRAM及其控制器等,视频编码 ASIC 的设计中,常将上述功能集成在一个芯片上,以SOC处理器的形式出现,如韩国 Intime 公司的 IM6410、深圳海思半导体有限公司的Hi3510、台湾台湾智原科技公司的FIC8120等。

FIC8120 是一个高集成度 SOC ,单个芯片内除了 ARM 核(FA526),MPEG-4 编/解码器外(FTMCP100),还集成了以太网 MAC 控制器、USB 控制器、IDE 控制器、SDRAM 控制器、CCIR-656 视频输入/输出等高速数据接口,另外还集成了 RS-232、 $I^2$ C、 $I^2$ S 等常用低速 I/O 接口。另外非常有特色的是,该芯片集成了 PCI 总线控制器,支持各种外部 PCI 扩展设备,这是很多基于 ARM 核的 SOC 所不具备的。PCI 对于功能扩展非常重要,例如通过扩展 802.11g 的 PCI 无线网卡,可以很方便地设计一个无线多媒体终端设备。

FIC8120 总体结构如图 2.16 所示。从图中可以看到,与众多其它 ARM 处理器一样,该 SOC 也采用了 AMBA 片内总线规范,片内各模块基于 AHB 和 APB 两级总线有机地组合为一个整体,其中 ARM 核、MPEG-4 编/解码器、SDRAM 控制器等高速设备挂在 AHB 总线上,而 RS-232、 $^{12}$ C 等低速设备挂在 APB 总线上。

网络化是嵌入式系统的发展趋势,很多 SOC 处理器都提供对网络的支持,一个完整的网络接口模块包括访问介质访问控制器(MAC)和物理层收发器(PHY)。同许多其它 SOC 一样,FIC8120 内部集成了 MAC 控制器,该 MAC 控制器是一个 AHB 主设备,兼容 IEEE 802.3 100Mbps 和 10Mbps,支持 MII 接口,具有 DMA 功能,通过 DMA 处理内部存储器与外部系统存储器之间的数据传输,确保足够的数据传输带宽。

图中 MPCA (Metal Programmable Cell Array)是一个可编程阵列,用户可基于 MPCA

定制特定的功能。在现有 SOC 设计中, MPCA 实现了 OSD (On-Screen Display)和色彩转换的功能。

图 2.16 MPEG-4 视频编/解码 SOC 结构

FIC8120 片内 MPEG-4 编/解码器是一个 AHB 设备,受片内 ARM 核的控制,在 D1 分辨率下支持 30 帧/秒的 simple profile 视频编码。在该模块内部集成了各种硬件算法加速器,如运动估计、运动补偿、DCT/IDCT、量化/反量化等。该编码器具有以下主要功能/性能:

- 兼容 MPEG-4 (ISO/IEC 14496-2) simple profile L0~L3 标准

- 支持 sub-QCIF、QCIF、CIF、VGA 及 4CIF 分辨率, 帧速率到达 30 帧/秒

- 兼容 JPEG (ISO/IEC 10918-1 ) base-line 标准

- 内部集成各种算法的硬件加速器,如运动估计/补偿、DCT/IDCT、量化/反量化、AC/DC 预测及变长编码/解码等

- 集成 DMA 控制器实现与系统存储器之间的高速数据传输

- 支持固定码率和可变码率控制

- 支持编码/解码的全双工模式

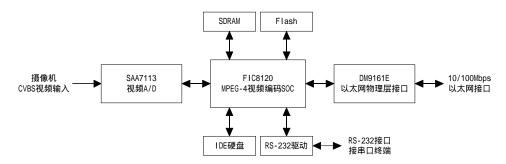

FIC8120 集成 CCIR-656 数字视频输入/输出接口。CCIR-656 输入接口用于视频采集,包括有两种应用方式,一种是"无缝"连接 CMOS 或 CCD 图像传感器,获取数字视频,常用于网络摄像机设计中;另一种是通过视频 A/D 模块(如 Philips 的 SAA7113)获取外部摄像机视频数据。CCIR-656 输出接口用于视频输出,实时的数字视频或解码后的数字视频数据通过这个接口送到外部的视频 D/A(如 Philips 的 SAA7126),转换成模拟信号送电视机显示。

FIC8120 是一种专用 SOC,以其为核心,可以很容易地设计出具有音、视频编码、存储、网络传输功能的嵌入式多媒体设备,如网络摄像机、小型数字视频录像机(DVR)等。图 2.17 给出的是一个基于该处理器的单通道小型 DVR 系统设计。FIC8120 支持全双工的语音/视频编码及输入/输出,图中所示系统基于具体应用的要求,在设计中没有保留视频输出接口和语音接口。

图 2.17 系统中采用 SAA7113 实现视频解码 (即 A/D), 该芯片是一个 CMOS 器件, 支持各种视频制式,能实现一路视频的 A/D, 支持标准的 CCIR-656 YUV 4:2:2 格式的数字视频输出,可与 FIC8120 "无缝"连接。该器件有最多四路视频输入,通过内部模拟开关

选择其中的一路进行处理。系统控制器通过  $I^2C$  总线对 SAA7113 进行控制。

FIC8120 通过 CCIR-656 数字视频接口获得 YUV 4:2:2 的原始视频数据,当视频源为 PAL 制式时分辨率为 720x576,当视频源为 NTSC 制式时分辨率为 720x480。根据功能需要,视频输入预处理单元可将输入的原始视频下采样为 CIF、QCIF 等各种分辨率。

图 2.17 基于 FIC8120 的单通道小型 DVR 系统设计

#### 2.9 嵌入式处理器的选择

嵌入式系统是为特定应用进行硬件、软件定制的专用计算机系统,应用千差万别,所以应用对嵌入式处理器的需求存在巨大差异,在设计一个新的嵌入式系统时,处理器的选择是一个需要仔细研究的问题。这一点和通用计算机处理器的选择有很大的区别,例如在为 PC 机选择处理器时,需要考虑的问题比较单纯,在价格承受的范围里,计算速度是选择处理器的最关键因素。

在嵌入式系统设计中,可能有多种处理器都可以满足系统的功能/性能要求,具体选择哪一种,往往需要综合考虑,在多种因素中取得一个平衡结果。

为嵌入式系统选择处理器需要考虑以下几个方面的因素:

# 1) 处理器性能

嵌入式处理器的性能取决于多个方面的因素,如字长、体系结构、时钟频率、cache设计、片内/片外总线带宽等。对于嵌入式系统中的处理器,一般并不过度最求性能,而是重点在于确保性能可以满足系统特定应用的需要,过高的性能往往伴随着成本的上升和功耗的增加。

#### 2) 处理器功能与接口

不同于 PC 机那样有着标准化的功能和接口,嵌入式系统硬件差异性很大,在为嵌入式选择处理器时,需要研究处理器提供的功能和接口。一般嵌入式处理器都会集成一些功能模块和接口控制器,如网络接口、LCD 显示接口、RS-232 串行接口、RTC、 $I^2$ C 等,使用这些内置的功能和接口,可以减少了整个系统芯片的数量,降低功耗、提高稳定性,而且开发减轻了系统开发工作量。

#### 3) 处理器的扩展能力

现在的嵌入式处理器集成度很高,但不能保证满足所有应用的要求,大多情况下,在应用中要为处理器扩展一些外部功能。实际设计中,要研究系统在存储芯片(RAM、Flash等)外部存储器(如 IDE 硬盘、SD 存储卡等)标准总线(如 PCI) A/D 接口控制、显示接口(如 VGA 显示接口、LCD 显示接口等)等功能扩展的需求,并以此作为处理器选型的一个依据。

#### 4) 处理器对内部存储器的支持

内部存储器是计算机的基本组成部分,嵌入式系统中的存储器有多种类型,常见的有

SRAM、SDRAM、NOR Flash、NAND Flash 等,嵌入式处理器对存储器类型的支持、寻址的能力、是否有足够容量的片内存储器等,是器件选型的一个重要因素。

#### 5) 处理器对网络的支持

网络化是嵌入式系统的一个发展趋势,对于需要支持网络接口的系统,在选择处理器时要考虑其对网络的支持能力,包括硬件支持和软件支持两个方面。硬件上,处理器要支持网络接口,一种方式是芯片内部集成网络控制器,另一种是外部扩展相关硬件模块;软件上,处理器需要支持相关网络协议,如 TCP/IP,协议可以附带在嵌入式操作系统中,也可以是在裸机上的驱动。

#### 6) 处理器的功耗与电源管理

嵌入式系统一般都有比较严格的功耗控制要求,尤其对于电池供电的系统,过高的功耗是致命性的问题。处理器往往是嵌入式系统中功耗最大的器件,在功耗要求严格的系统中,处理器一定要用低功耗的类型。另外,如果处理器支持灵活的电源管理,将有利于控制系统的运行功耗,如在任务执行过程中,系统全速运行,而在空闲期间,处理器可以控制系统进入睡眠状态、甚至掉电状态,从而显著地降低系统总功耗。

#### 7) 处理器的环境适应性

嵌入式系统都有特定的应用环境,处理器必须能够适应系统环境的要求。工作温度范围是一个非常重要的指标,民用级、工业级和军用级的处理器工作温度范围不一样。另外一些特殊的应用有特殊的环境要求,如在航天器中,处理器可能还需要有防空间辐射的要求。

# 8) 操作系统的支持

在功能简单的嵌入式系统中,不需要运行操作系统,但对于那些复杂功能的系统,嵌入式操作系统可能是必不可少的软件平台,在这种情况下,选择处理器时要考虑其是否支持嵌入式操作系统,支持的操作系统是否满足系统设计的要求。

#### 9) 软件资源是否丰富

在嵌入式系统的设计过程中,软件开发的工作量很大,为了缩短开发周期,提高软件的可靠性,经常需要充分利用已有成熟、可靠的软件资源,如协议栈(如 H.323 协议栈、SIP 协议栈、TCP/IP 协议栈等) 设备驱动程序、甚至操作系统下的应用软件。

# 10) 软件开发工具

嵌入式软件的开发包括代码编辑、编译、链接、调试几个阶段,一般采用交叉开发的方法,在开发机上设计软件并生成目标机的可执行代码,在目标机上调试运行。开发过程复杂,涉及很多的软件工具,所以嵌入式处理器一般有对应的软件集成开发环境(IDE),将软件开发过程设计的所有工具集成在一个图形化的开发平台中。功能完善、界面友善的IDE 可以使软件的开发工作事半功倍。

#### 11) 处理器支持的调试接口

嵌入式系统开发中软件调试、下载及系统测试是一个非常重要的工作,为此很多处理器提供灵活的调试接口,通过这个接口,使用专门的开发工具可以将运行代码下载到目标机中,并可跟踪软件的运行,随时查看处理器的寄存器和系统存储器的内容。友好的调试接口为嵌入式系统开发提供有力的支持,常见的调试接口是 JTAG。

#### 12) 处理器的封装形式

嵌入式系统往往需要定制硬件,涉及到 PCB 设计、生产及元/器件焊接。在实际工作中芯片的封装是个需要考虑的问题。元/器件封装有穿孔直插和表面贴装两种,表面组装技术具有组装密度高,可靠性高,高频性能好、可以降低成本、便于自动化生产等优点。嵌入式处理器越来越多地采用表面贴装的封装形式,如 OFP、SOP、PLCC、BGA 等,选择

处理器封装要考虑 PCB 元件密度、焊接成本、调试要求等因素。

13) 处理器的评估板/开发板

评估板为处理器提供一个功能评测的实际平台,通常也是一个很好的软、硬件件参考设计。对于一个系统开发团队不熟悉的处理器型号来说,评估板有着尤其重要的作用。通过对评估板的测试,可对处理器的功能、性能有客观的认识,从而指导处理器的选型。另外,评估板也可以作为具体应用设计的参考,极大地降低系统开发的难度,缩短开发周期。

14) 处理器成本及系统综合成本

通常成本是嵌入式系统开发需要考虑的关键问题,选择处理器当然要考虑价格因素。 分析成本时,不能仅看处理器本身,要看系统综合成本。有时候一种处理器价格低,但外 部需要扩充一些控制器,而另一种处理器价格高,可需要的控制器已经集成在芯片内,这 时候要分析系统的综合成本。

- 15) 应用的普遍性、稳定性、可靠性

- 一般来说,权威厂家的处理器产品、或是经过长期、广泛应用的处理器产品技术支持好,而且稳定性、可靠性经过普遍验证,值得信赖。对于新推出的处理器或冷门处理器,选用前要做好充分的论证和测试。

- 16) 项目开发人员对产品的熟悉程度

产品是人设计出来的,选择开发人员熟悉的处理器,可以降低开发风险、缩短开发周期。

17) 产品供货供货周期和生命期

选择的处理器产品供货周期必须要满足系统开发、生产的要求。另外,嵌入式处理器产品的生命期要长,能够稳定地提供产品生产、再生产以及后续维护、维修的产品供货。

#### 2.10 嵌入式处理器的 JTAG 调试接口

调试是利用可控的软件和硬件手段完成对嵌入式系统软件和硬件功能及正确性检测的过程。嵌入式处理器最常用最有效的调试方式是采用 JTAG 调试技术,通过 JTAG 接口,不需要在目标系统上运行任何监控程序,就可实现对目标系统调试的功能。JTAG 调试接口几乎是各种高性能处理器的标准配置,如 ARM、MIPS 处理器,以及各种 DSP、FPGA 等芯片。

JTAG (Joint Test Action Group)原指联合测试行动组织,该组织最早提出了一种测试访问端口和边界扫描体系结构(Test Access Port and Boundary Scan Architecture),JTAG 调试技术也即边界扫描技术,它是在靠近芯片的输入、输出引脚上插入一个移位寄存器(也称边界扫描单元),通过这个寄存器,可以把外部信号(数据)加载到该管脚中去,也可以"捕获"该管脚上的输出信号,从而完全控制芯片的工作,达到调试的目的。这些边界扫描寄存器单元相互串接,在芯片周围形成一条链,称扫描链。数据通过扫描链从 JTAG的 TDI 引入,TDO 引出,它一方面将 JTAG 电路与内核逻辑电路联系起来,另一方面又隔离内核电路与芯片引脚。通过不同功能的扫描链,可以实现不同的在线仿真功能。

JTAG 有五个接口信号: TCK、TMS、TDI、TDO 和 TRST。

TRST (Test Reset Input): 用来对 JTAG 接口控制器进行复位,它不是必须的,通过在TMS 脚也可以实现 JTAG 复位功能。

TCK (Test Clock Input):为 JTAG 接口控制器提供了一个独立的、基本的时钟信号, JTAG 接口所有操作都是通过这个时钟信号来驱动的。

TMS (Test Mode Selection Input):用来控制 JTAG 接口控制器状态机的转换。通过TMS 信号,可以控制 JTAG 接口在不同的状态间相互转换。TMS 信号在 TCK 的上升沿有

效。

Test Data Input (TDI):数据输入的接口。所有要输入到 JTAG 特定寄存器的数据都通过 TDI 接口在 TCK 的同步下一位一位地串行输入。

Test Data Output (TDO):数据输出的接口。所有要从 JTAG 特定寄存器中输出的数据 都通过 TDO 接口在 TCK 的同步一位一位串行输出。

JTAG 在嵌入式系统开发过程中有重要的作用,主要包括以下几个方面:

- 1) 硬件基本功能的测试。通过 JTAG,可以读写处理器内部的寄存器,设置 I/O 引脚的状态,通过这些操作,可对处理器的基本工作状态进行判断。另外通过 JTAG可以读写处理器外部的存储器单元,可以在不编写测试程序的情况下对系统内存基本功能进行测试。

- 2) 软件下载。嵌入式系统软件一般采用交叉开发的方式,在开发机中生成目标机的运行代码后,可通过 JTAG 下载到目标机中运行。这种代码下载不需要目标机中有任何程序的支持。

- 3) 软件调试。运行代码下载到嵌入式目标机后,通过 JTAG 接口,开发机的调试工具可以对目标代码的运行进行跟踪、设置断点、查看/修改寄存器值等调试操作。

- 4) Flash 烧写。 通过 JTAG 口, 开发机可把最终的运行代码烧写到目标机的 Flash 中。

#### 参考文献

苏伟斌编著,8051 系列单片机应用手册,科学出版社,1997 杜春雷编著,ARM 体系结构与编程,清华大学出版社,2003 年 2 月第 1 版